36

Super X11DAC User's Manual

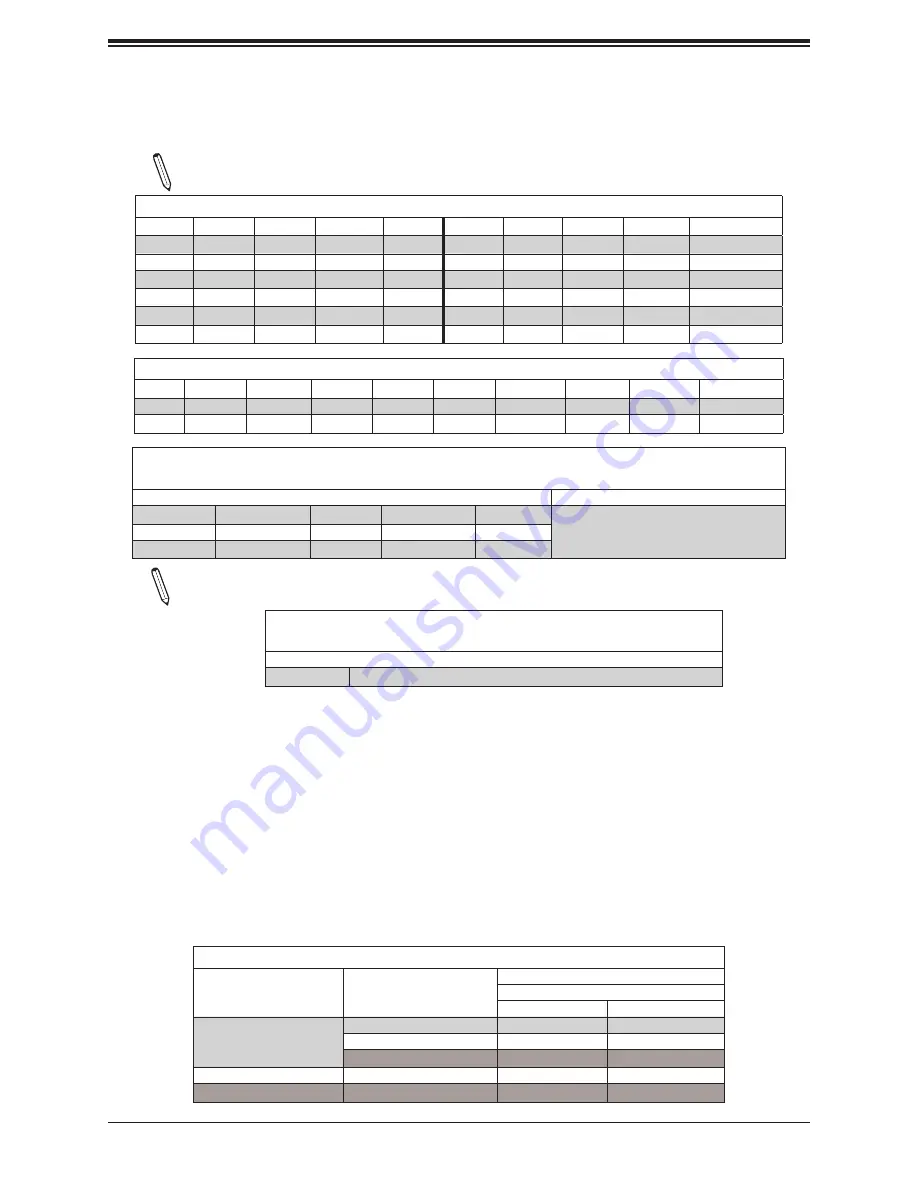

DCPMM Memory Population Tables for 2nd Gen Intel Xeon Scalable-SP

Processors

Validation Matrix (DDR4 DIMMs Validated w/DCPMM)

DIMM Type

Ranks Per DIMM

& Data Width

(Stack)

DIMM Capacity (GB)

DRAM Density

4Gb

8Gb

RDIMM

1Rx4

8GB

16GB

2Rx8

8GB

16GB

2Rx4

16GB

32GB

LRDIMM

4Rx4

N/A

64GB

LRDIMM 3DS

8Rx4 (4H)

N/A

128GB

Symmetric Population within 1 CPU Socket

Modes

P1-DIMMF1 P1-DIMME1

P1-DIMMD1

P1-DIMMD2 P1-DIMMA2 P1-DIMMA1 P1-DIMMB1

P1-DIMMC1

Channel Config.

AD

DRAM1

DRAM1

DRAM1

DCPMM

DCPMM

DRAM1

DRAM1

DRAM1

2-1-1

MM

DRAM2

DRAM2

DRAM2

DCPMM

DCPMM

DRAM2

DRAM2

DRAM2

2-1-1

AD + MM

DRAM3

DRAM3

DRAM3

DCPMM

DCPMM

DRAM3

DRAM3

DRAM3

2-1-1

AD

DCPMM

DRAM1

DRAM1

-

-

DRAM1

DRAM1

DCPMM

1-1-1

MM

DCPMM

DRAM1

DRAM1

-

-

DRAM1

DRAM1

DCPMM

1-1-1

AD + MM

DCPMM

DRAM3

DRAM3

-

-

DRAM3

DRAM3

DCPMM

1-1-1

Asymmetric Population within 1 CPU Socket

Modes

P1-DIMMF1

P1-DIMME1

P1-DIMMD1 P1-DIMMD2 P1-DIMMA2

P1-DIMMA1

P1-DIMMB1

P1-DIMMC1

Channel Config.

AD

DRAM1

DRAM1

DRAM1

-

DCPMM

DRAM1

DRAM1

DRAM1

2-1-1

AD*

DRAM1

DRAM1

DRAM1

-

DCPMM

DRAM1

DRAM1

DRAM1

2-1-1

Legend

(for the two tables above)

DDR4 Type

Capacity

DRAM1

RDIMM

3DS RDIMM

LRDIMM

3DS LRDIMM

Refer to Validation Matrix (DDR4 DIMMs validated with

DCPMM) below.

DRAM2

RDIMM

-

-

-

DRAM3

RDIMM

3DS RDIMM

LRDIMM

-

Note

: DDR4 single rank x8 is not available for DCPMM Memory Mode or App Direct Mode.

Legend

(for the first two tables above)

Capacity

DCPMM

Any Capacity (Uniformly for all channels for a given configuration)

•

* 2nd socket has no DCPMM DIMM

•

Mode definitions: AD=App Direct Mode, MM=Memory Mode, AD+MM=Mixed Mode.

•

For MM, general DDR4+DCPMM ratio is between 1:4 and 1:16. Excessive capacity for DCPMM can be used for AD.

•

For each individual population, rearrangements between channels are allowed as long as the resulting population is

compliant with the X11 memory population use for the 2nd Gen Intel Xeon Scalable-SP processors.

•

For each individual population, please use the same DDR4 DIMM in all slots.

•

For each individual population, sockets are normally symmetric with exceptions for 1 DCPMM per socket and 1 DCPMM

per node case. Currently, DCPMM modules operate at 2666 MHz.

•

No mixing of DCPMM and NVMDIMMs within the same platform is allowed.

•

These DCPMM population tables target a balanced DCPMM-to-DRAM-cache ratio in MM and MM + AD modes.

Note:

Only 2nd Gen Intel Xeon Scalable-SP (82xx/62xx/52xx/4215 series) processors

support DCPMM memory.