108

M3i.48xx / M3i.48xx-exp Manual

Timestamp modes

Timestamps

Timestamp modes

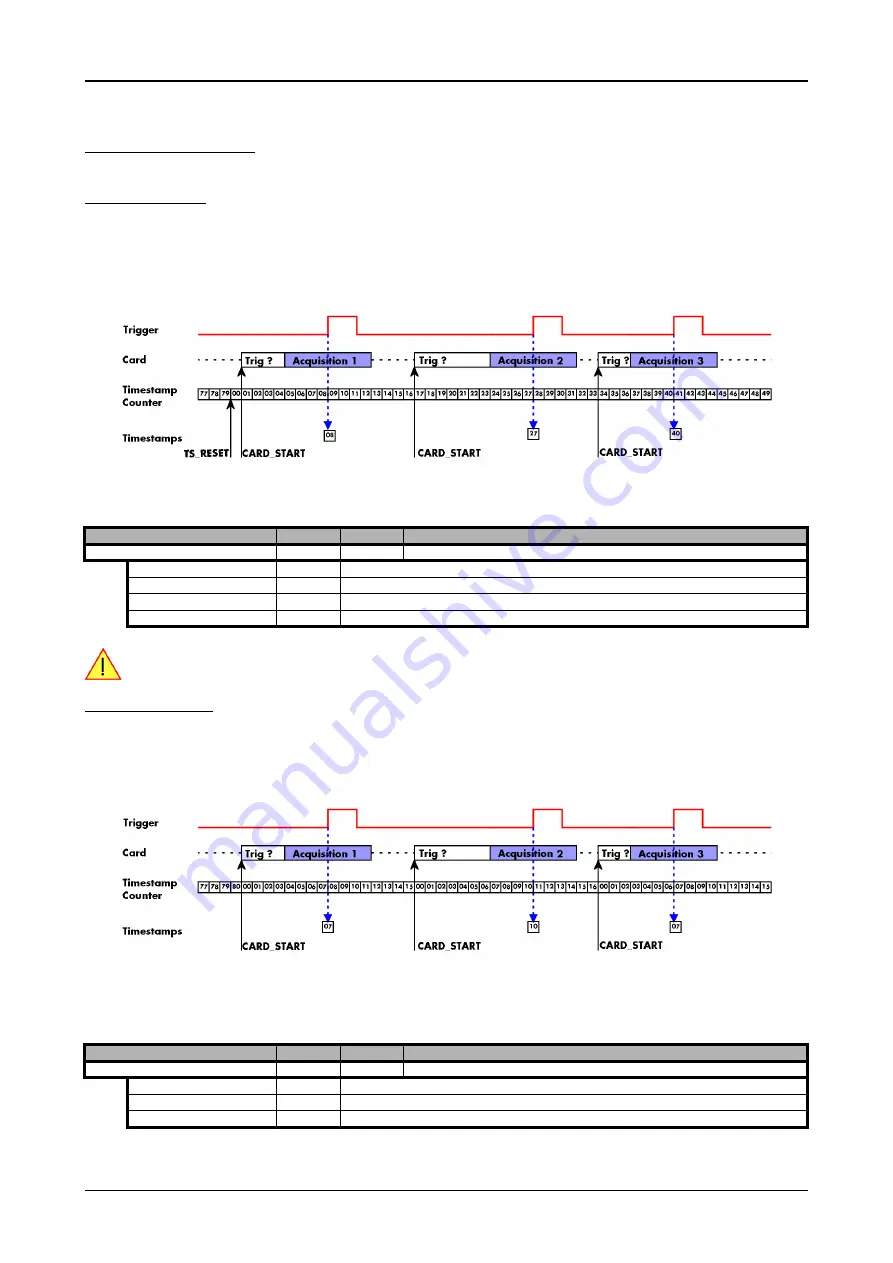

Standard mode

In standard mode the timestamp counter is set to zero once by writing the TS_RESET commando to the command register. After that command

the counter counts continuously independent of start and stop of acquisition. The timestamps of all recorded trigger events are referenced to

this common zero time. With this mode you can calculate the exact time difference between different recordings and also within one acqui-

sition (if using Multiple Recording or Gated Sampling).

The following table shows the valid values that can be written to the timestamp command register for this mode:

Please keep in mind that this mode only work sufficiently as long as you don’t change the sampling rate

between two acquisitions that you want to compare.

StartReset mode

In StartReset mode the timestamp counter is set to zero on every start of the card. After starting the card the counter counts continuously. The

timestamps of one recording are referenced to the start of the recording. This mode is very useful for Multiple Recording and Gated Sampling

(see according chapters for detailed information on these two optional modes)

The following table shows the valid values that can be written to the timestamp command register.

Register

Value

Direction

Description

SPC_TIMESTAMP_CMD

47000

read/write

Programs a timestamp mode and performs commands as listed below

SPC_TSMODE_DISABLE

0

Timestamp is disabled.

SPC_TS_RESET

1h

The timestamp counter is set to zero

SPC_TSMODE_STANDARD

2h

Standard mode, counter is reset by explicit reset command.

SPC_TSCNT_INTERNAL

100h

Counter is running with complete width on sampling clock

Register

Value

Direction

Description

SPC_TIMESTAMP_CMD

47000

read/write

Programs a timestamp mode and performs commands as listed below

SPC_TSMODE_DISABLE

0

Timestamp is disabled.

SPC_TSMODE_STARTRESET

4h

Counter is reset on every card start, all timestamps are in relation to card start.

SPC_TSCNT_INTERNAL

100h

Counter is running with complete width on sampling clock