SN8P275X Series

8-bit micro-controller build-in 12-bit ADC

SONiX TECHNOLOGY CO., LTD

Page 129

Version 0.7

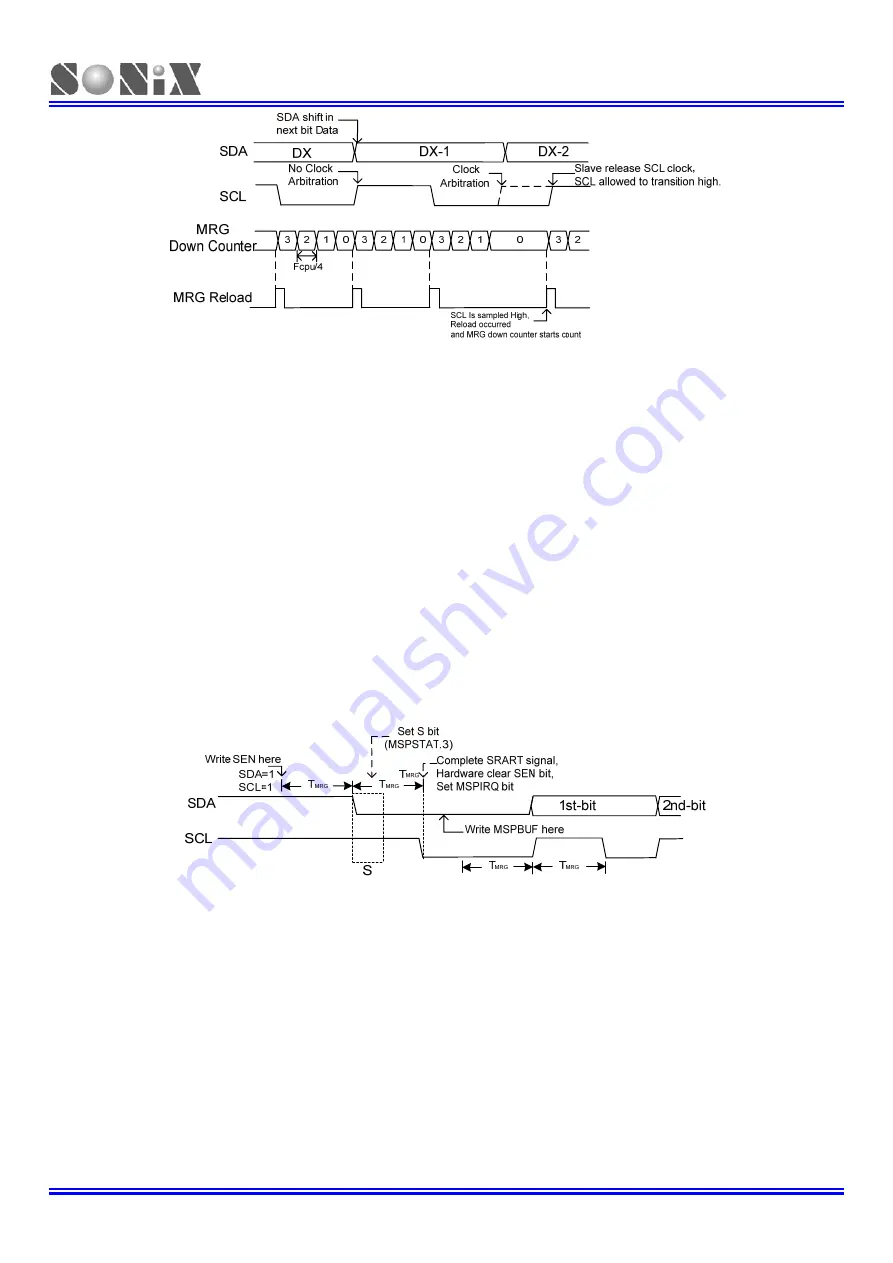

MRG Timing Diagram with and without Clock Arbitration (MSPADRR=0x03)

10.8.3 MSP Mater START Condition

To generate a START signal, user sets SEN bit (MSPM2.0). When SDA and SCL pin are both sampled High, MSP rate

generator reload MSPADDR[6:0], and starts down counter. When SDA and SCL are both sampled high and MRG

overflow, SDA pin is drive low. When SCL sampled high, and SDA transmitted from High to Low is the START signal

and will set S bit (MSPSTAT.3). MRG reload again and start down counter. SEN bit will be clear automatically when

MRG overflow, the MRG is suspend leaving SDA line held low, and START condition is complete.

z

WCOL Status Flag

If user write to MSPBUF when START condition processing, then WCOL is set and the content of MSPBUF data is

un-changed. (the writer doesn’t occur)

START Condition Timing Diagram