000-0046140-111

Page 48 of 169

SLG46140

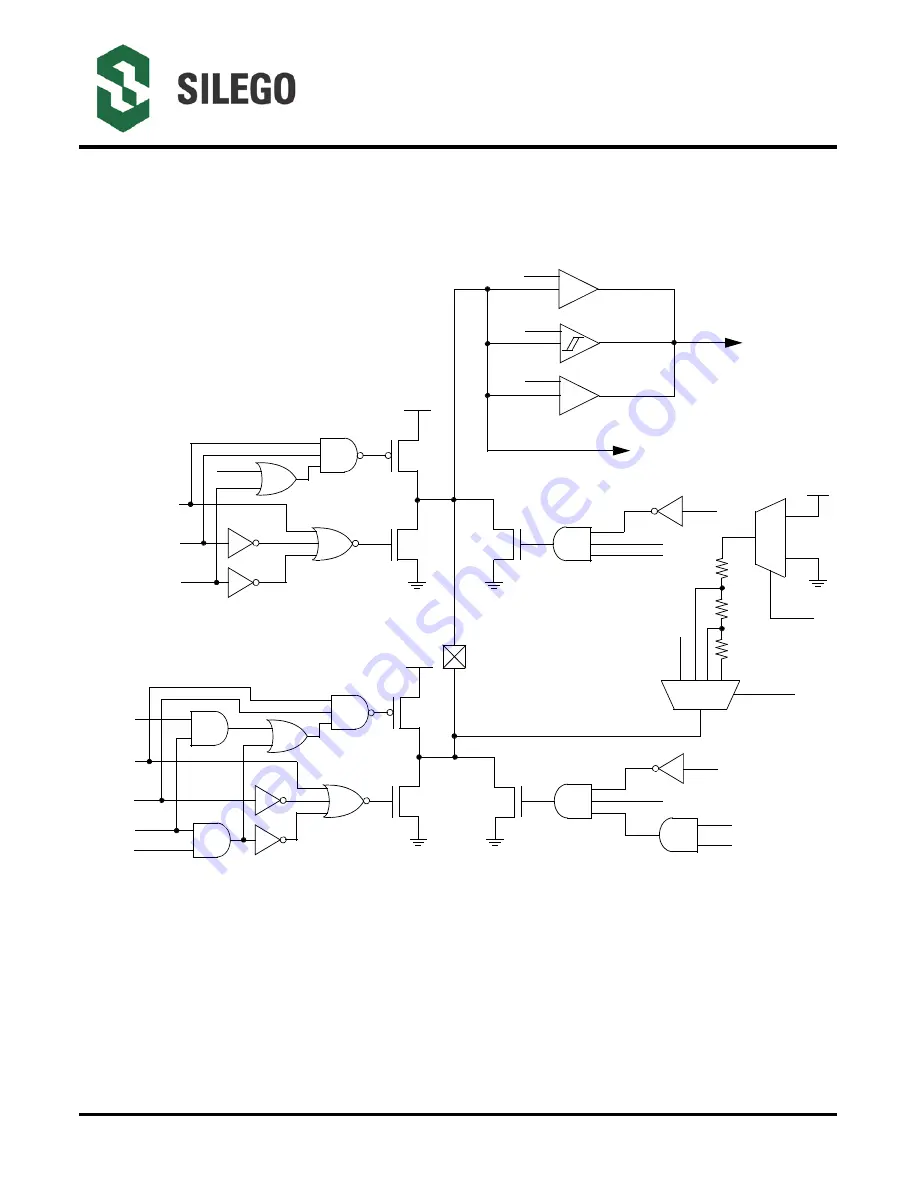

7.7 Register OE IO Structure

7.7.1 Register OE IO Structure (for Pins 6, 11)

Figure 5. Register OE IO Structure Diagram

PAD

Digital In

S0

S1

S2

S3

Flo

a

ting

S0

S1

pull_up_en

10 k

90 k

900 k

Res_sel[1:0]

00: floating

01: 10 k

10: 100 k

11: 1 M

wosmt_en

smt_en

lv_en

Low Voltage

Input

Schmitt Trigger

Input

Non-Schmitt

Trigger Input

Mode [2:0]

000: Digital In without Schmitt Trigger, wosmt_en=1, OE = 0

001: Digital In with Schmitt Trigger, smt_en=1, OE = 0

010: Low Voltage Digital In mode, lv_en = 1, OE = 0

011: analog IO mode

100: push-pull mode, pp_en=1, OE = 1

101: NMOS open drain mode, odn_en=1, OE = 1

110: PMOS open drain mode, odp_en=1, OE = 1

111: analog IO and NMOS open-drain mode, odn_en=1 and AIO_en=1

Analog IO

Digital Out

Digital Out

OE

odn_en

OE

odn_en

2x_en

Digital Out

OE

pp_en

odp_en

Digital Out

OE

pp_en

2x_en

odp_en