254

APPENDIX A DEVELOPMENT TOOLS

User’s Manual U15104EJ2V0UD

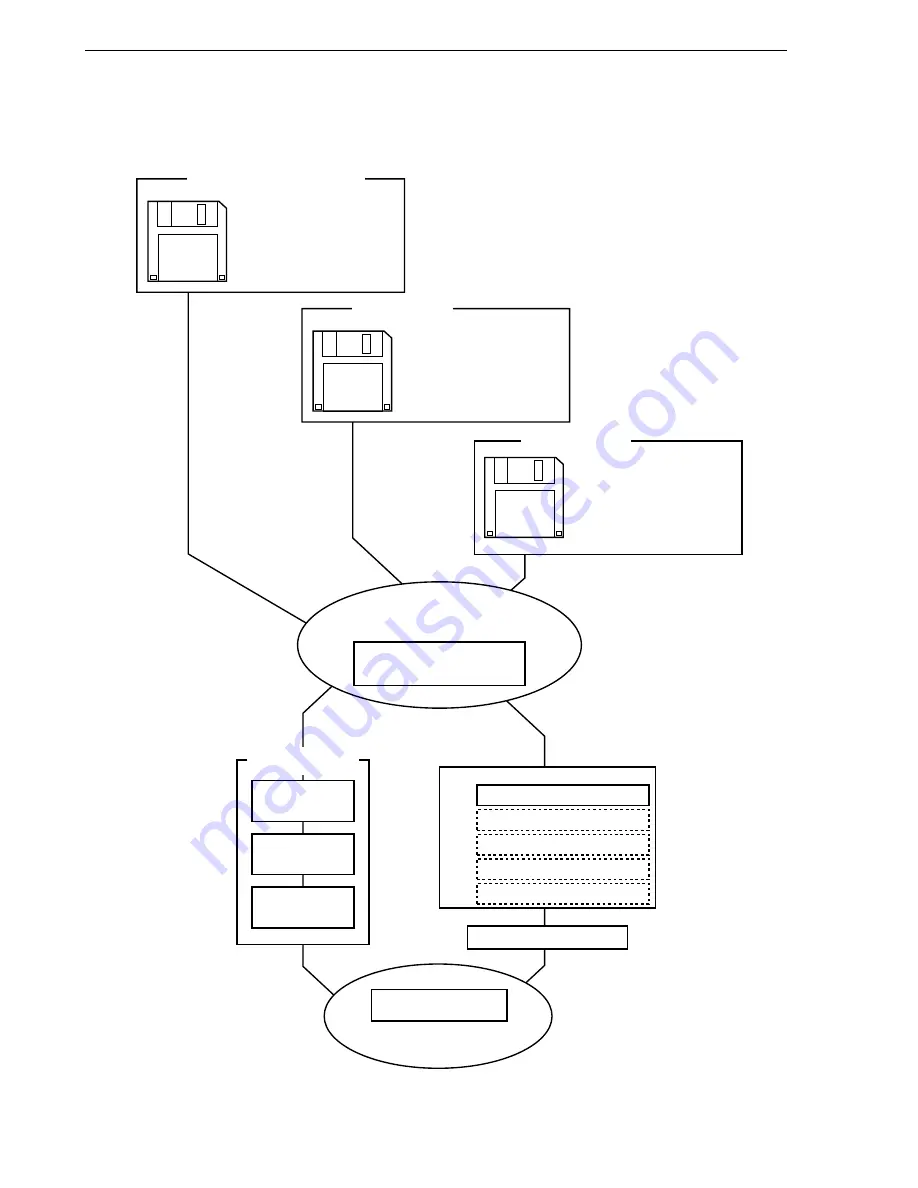

Figure A-1. Configuration of Development Tools (2/2)

(2) When using the in-circuit emulator IE-78001-R-A

Remark

Items in broken line boxes differ according to the development environment. Refer to A.5 Debugging

Tools (Hardware).

• System simulator

• Integrated debugger

• Device file

Embedded Software

• Real-time OS

• OS

Debugging Tool

• Assembler package

• C compiler package

• C library source file

• Device file

Language Processing Software

Flash memory

write adapter

In-Circuit Emulator

Emulation probe

Conversion socket or

conversion adapter

Target system

Host Machine (PC or EWS)

Interface board

Interface adapter

Emulation board

I/O board

Probe board

Emulation probe conversion board

On-chip flash

memory version

Flash Memory

Write Environment

Flash programmer