CHAPTER 10 A/D CONVERTER

Preliminary User’s Manual U16898EJ1V0UD

165

10.4.3 A/D converter operation mode

The operation mode of the A/D converter is the select mode. One channel of analog input is selected from ANI0 to

ANI3 by the analog input channel specification register (ADS) and A/D conversion is executed.

(1) A/D conversion operation

By setting bit 7 (ADCS) of the A/D converter mode register (ADM) to 1, the A/D conversion operation of the

voltage, which is applied to the analog input pin specified by the analog input channel specification register

(ADS), is started.

When A/D conversion has been completed, the result of the A/D conversion is stored in the A/D conversion result

register (ADCR, ADCRH), and an interrupt request signal (INTAD) is generated. Once the A/D conversion has

started and when one A/D conversion has been completed, the next A/D conversion operation is immediately

started. The A/D conversion operations are repeated until new data is written to ADS.

If ADM or ADS is written during A/D conversion, the A/D conversion operation under execution is stopped and

restarted from the beginning.

If 0 is written to ADCS during A/D conversion, A/D conversion is immediately stopped. At this time, the

conversion result is undefined.

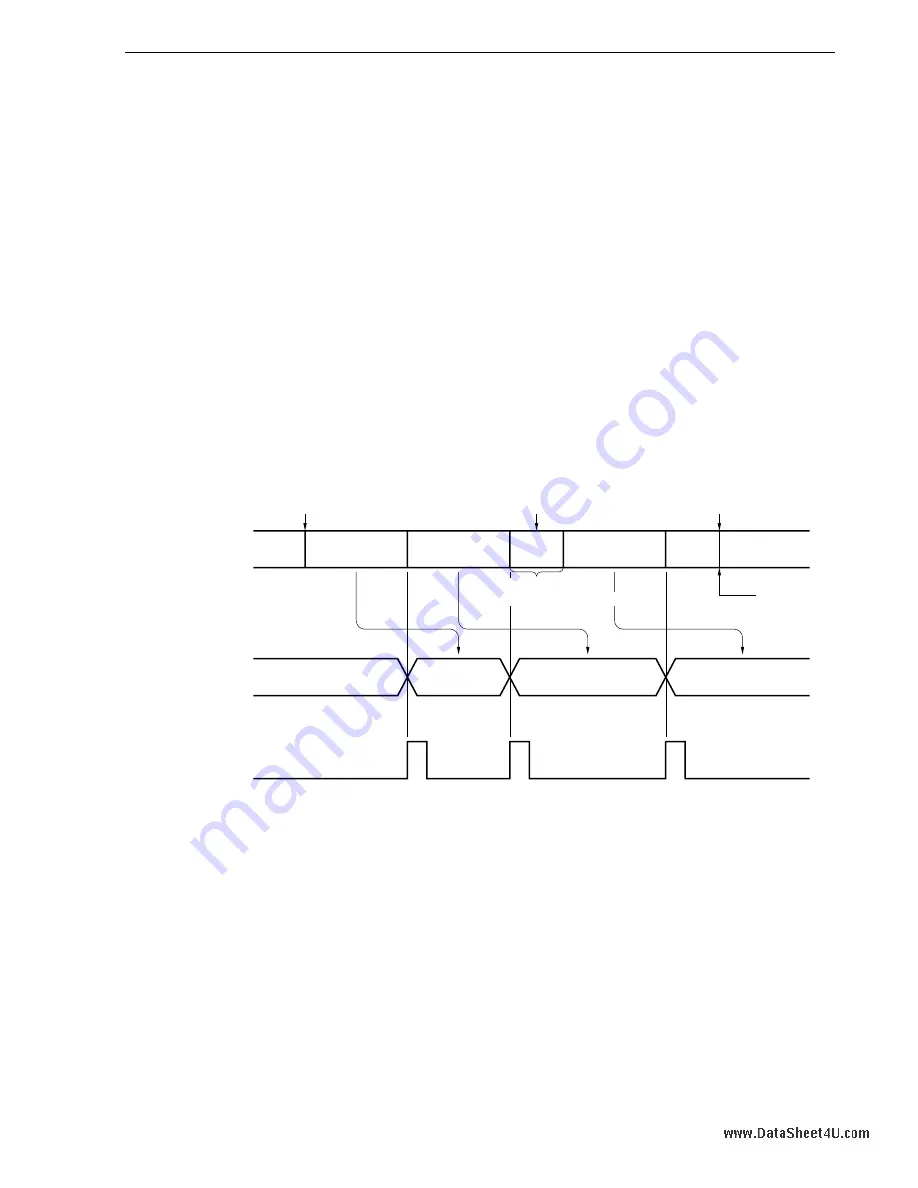

Figure 10-13. A/D Conversion Operation

ANIn

Rewriting ADM

ADCS = 1

Rewriting ADS

ADCS = 0

ANIn

ANIn

ANIn

ANIm

ANIn

ANIm

ANIm

Stopped

A/D conversion

ADCR,

ADCRH

INTAD

Conversion is stopped

Conversion result is not retained

Remarks 1. n = 0 to 3

2. m = 0 to 3

www.DataSheet4U.com

www.DataSheet4U.com