RTE-V830-PC

USER’ S MANUAL

21

7. JEXT BUS SPECIFICATION

The JEXT is a connector which is used to expand memory and I/O units. The local bus on this

board is connected to the JEXT connector.

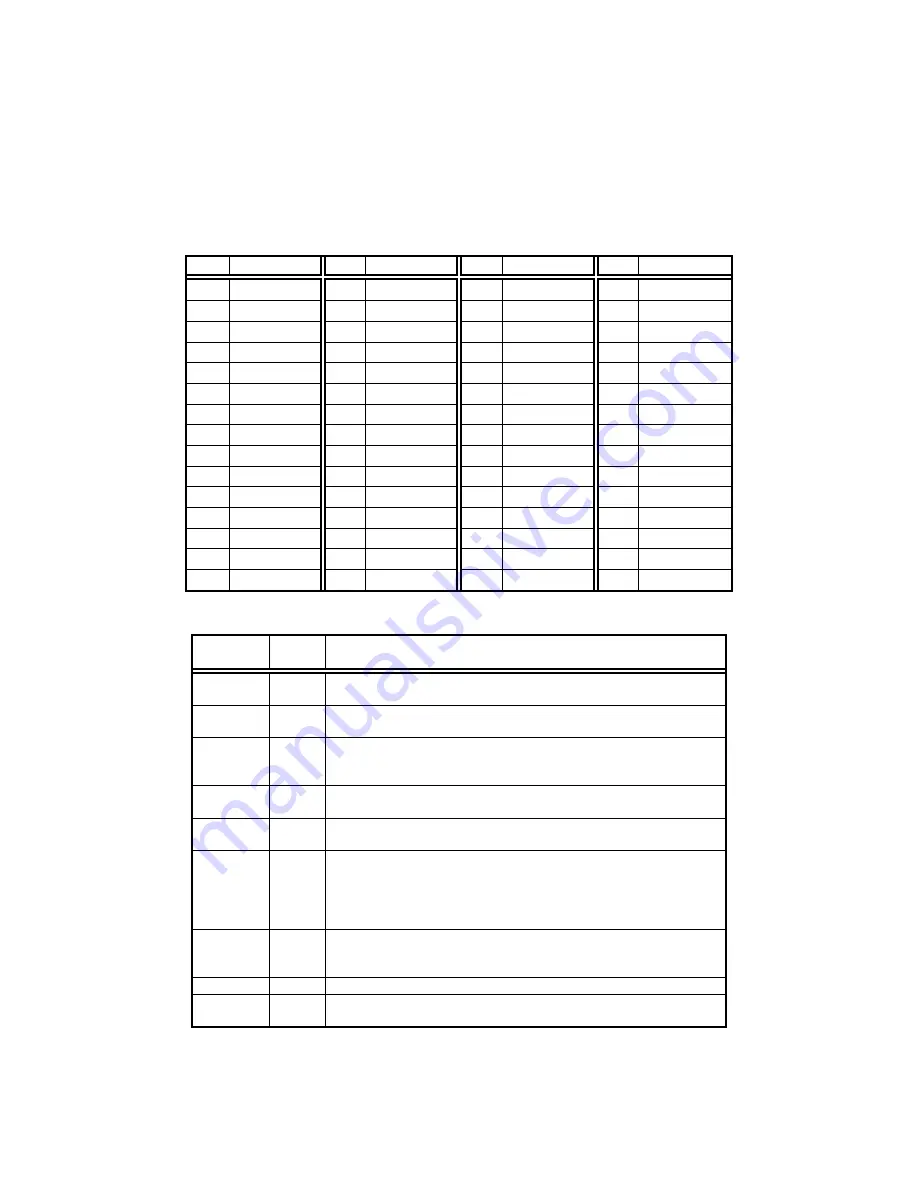

The following tables list the pin arrangement of the JEXT connector and the functions of each

signal. The timing relationships between the signals are also shown below.

Number

Signal name

Number

Signal name

Number

Signal name

Number

Signal name

1

+5V

2

+5V

31

GND

32

GND

3

D0

4

D1

33

A8

34

A9

5

D2

6

D3

35

A10

36

A11

7

D4

8

D5

37

A12

38

A13

9

D6

10

D7

39

A14

40

A15

11

GND

12

GND

41

+5V

42

+5V

13

D8

14

D9

43

A16

44

A17

15

D10

16

D11

45

A18

46

A19

17

D12

18

D13

47

BHE-

48

GND

19

D14

20

D15

49

GND

50

RD-

21

+5V

22

+5V

51

WR-

52

RESET-

23

A0

24

A1

53

GND

54

GND

25

A2

26

A3

55

READY

56

INT-

27

A4

28

A5

57

GND

58

GND

29

A6

30

A7

59

CPUCLK

60

GND

JEXT Connector Pin Arrangement

Signal

name

Input/

output

Function

A[0..19]

Output

Address bus signal, which is originally the CPU address signal

received at a buffer.

BHE-

Output

Byte high enable signal, which is originally the CPU UBE- signal

received at a buffer.

D[0..15]

Input/

output

Data bus signal, which is originally the CPU data bus signal received

at a buffer.

It is pulled up with a 10 k

Ω

resistor on the board.

RD-

Output

Read cycle timing signal, which becomes active only when the JEXT

space is accessed.

WR-

Output

Write cycle timing signal, which becomes active only when the JEXT

space is accessed.

READY

Input

Signal indicating the end of a cycle. It is valid only for the JEXT

space.

To have the CPU recognize READY securely, it is necessary to keep

READY active until RD- or WR- becomes inactive. It is pulled up

with a 10 k

Ω

resistor on the board.

INT-

Input

Active-low interrupt request signal, which is connected to the INT pin

of the CPU via a interrupt controller(vector 11 is occurred). It is

pulled up with a 10 k

Ω

resistor on the board.

RESET-

Output

Active-low system reset signal

CLK

Output

Clock signal, which is connected to the CLKOUT pin of the V830 via

a buffer.

JEXT Connector Signals