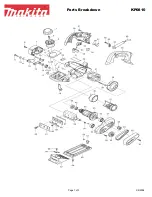

46

1

FEATURES

APPLICATIONS

Xin/CLK

1

14

Xout

S0

2

13

S1/SDA

V

DD 3

12

S2/SCL

V

ctr 4

11

Y1

GND

5

10

GND

V

DDOUT 6

9

Y2

7

8

Y3

VCXO

XO

LVCMOS

LV

CMOS

LV

CMOS

PLL

with�SSC

LV

CMOS

Divider

and

Output

Control

3

EEPROM

Programming

and

Control�Register

V

ctr

Crystal�or

Clock�Input

S2/S1/S0�or

SDA/SCL

V

DD

GND

V

DDOUT

Y1

Y2

Y3

V

DDOUT

CDCE913

CDCEL913

SCAS849B–JUNE 2007–REVISED DECEMBER 2007

www.ti.com

Programmable 1-PLL VCXO Clock Synthesizer With 1.8-V, 2.5-V, and 3.3-V Outputs

•

Flexible Clock Driver

2345

•

Member of Programmable Clock Generator

– Three User-Definable Control Inputs

Family

[S0/S1/S2], for example., SSC Selection,

Frequency Switching, Output Enable, or

–

CDCE913/CDCEL913: 1-PLL, 3 Outputs

Power Down

– CDCE925/CDCEL925: 2-PLL, 5 Outputs

– Generates Highly Accurate Clocks for

– CDCE937/CDCEL937: 3-PLL, 7 Outputs

Video, Audio, USB, IEEE1394, RFID,

– CDCE949/CDCEL949: 4-PLL, 9 Outputs

Bluetooth™, WLAN, Ethernet™, and GPS

•

In-System Programmability and EEPROM

– Generates Common Clock Frequencies

– Serial Programmable Volatile Register

Used With TI-DaVinci™, OMAP™, DSPs

– Nonvolatile EEPROM to Store Customer

– Programmable SSC Modulation

Setting

– Enables 0-PPM Clock Generation

•

Flexible Input Clocking Concept

•

1.8-V Device Power Supply

– External Crystal: 8 MHz to 32 MHz

•

Wide Temperature Range –40

°

C to 85

°

C

– On-Chip VCXO: Pull Range ±150 ppm

•

Packaged in TSSOP

– Single-Ended LVCMOS up to 160 MHz

•

Development and Programming Kit for Easy

•

Free Selectable Output Frequency up to

PLL Design and Programming (TI Pro-Clock™)

230 MHz

•

Low-Noise PLL Core

•

D-TV, STB, IP-STB, DVD-Player, DVD-Recorder,

– PLL Loop Filter Components Integrated

Printer

– Low Period Jitter (Typical 50 ps)

•

Separate Output Supply Pins

– CDCE913: 3.3 V and 2.5 V

– CDCEL913: 1.8 V

1

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of

Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

2

DaVinci, OMAP, Pro-Clock are trademarks of Texas Instruments.

3

Bluetooth is a trademark of Bluetooth SIG.

4

I2C is a trademark of Philips Electronics.

5

Ethernet is a trademark of Xerox Corporattion.

PRODUCTION DATA information is current as of publication date.

Copyright © 2007, Texas Instruments Incorporated

Products conform to specifications per the terms of the Texas

Instruments standard warranty. Production processing does not

necessarily include testing of all parameters.

www.ti.com

DESCRIPTION

CDCE913

CDCEL913

SCAS849B–JUNE 2007–REVISED DECEMBER 2007

These devices have limited built-in ESD protection. The leads should be shorted together or the device placed in conductive foam

during storage or handling to prevent electrostatic damage to the MOS gates.

The CDCE913 and CDCEL913 are modular PLL-based low-cost, high-performance, programmable clock

synthesizers, multipliers, and dividers. They generate up to 3 output clocks from a single input frequency. Each

output can be programmed in-system for any clock frequency up to 230 MHz, using the integrated configurable

PLL.

The CDCx913 has separate output supply pins, V

DDOUT

, which is 1.8 V for CDCEL913 and 2.5 V to 3.3 V for

CDCE913.

The input accepts an external crystal or LVCMOS clock signal. If an external crystal is used, an on-chip load

capacitor is adequate for most applications. The value of the load capacitor is programmable from 0 to 20 pF.

Additionally, an on-chip VCXO is selectable which allows synchronization of the output frequency to an external

control signal, that is, PWM signal.

The deep M/N divider ratio allows the generation of zero-ppm audio/video, networking (WLAN, BlueTooth,

Ethernet, GPS) or interface (USB, IEEE1394, Memory Stick) clocks from e.g., a 27 MHz reference input

frequency.

The PLL supports SSC (spread-spectrum clocking). SSC can be center-spread or down-spread clocking which is

a common technique to reduce electro-magnetic interference (EMI).

Based on the PLL frequency and the divider settings, the internal loop filter components are automatically

adjusted to achieve high stability and optimized jitter transfer characteristic.

The device supports non-volatile EEPROM programming for ease customization of the device to the application.

It is preset to a factory default configuration (see the

DEFAULT DEVICE CONFIGURATION

section). It can be

re-programmed to a different application configuration before PCB assembly, or re-programmed by in-system

programming. All device settings are programmable through SDA/SCL bus, a 2-wire serial interface.

Three programmable control inputs, S0, S1 and S2, can be used to select different frequencies, or change SSC

setting for lowering EMI, or other control features like, outputs disable to low, outputs 3-state, power down, PLL

bypass etc).

The CDCx913 operates in a 1.8 V environment. It operates in a temperature range of –40

°

C to 85

°

C.

Terminal Functions for CDCE913, CDCEL913

TERMINAL

I/O

DESCRIPTION

NAME

PIN TSSOP14

Y1–Y3

11, 9, 8

O

LVCMOS outputs

Xin/CLK

1

I

Crystal oscillator input or LVCMOS clock Input (selectable via SDA/SCL bus)

Xout

14

O

Crystal oscillator output (leave open or pullup when not used)

V

Ctrl

4

I

VCXO control voltage (leave open or pullup when not used)

V

DD

3

Power

1.8-V power supply for the device

CDCEL913

: 1.8-V supply for all outputs

V

DDOUT

6, 7

Power

CDCE913:

3.3-V or 2.5-V supply for all outputs

GND

5, 10

Ground Ground

S0

2

I

User-programmable control input S0; LVCMOS inputs; internal pullup 500k

SDA:

bidirectional serial data input/output (default configuration), LVCMOS internal

SDA/S1

13

I/O or I

pullup; or

S1:

user-programmable control input; LVCMOS inputs; internal pullup 500k

SCL:

serial clock input LVCMOS (default configuration), internal pullup 500k or

SCL/S2

12

I

S2:

user-programmable control input; LVCMOS inputs; internal pullup 500k

2

Submit Documentation Feedback

Copyright © 2007, Texas Instruments Incorporated

Product Folder Link(s):

CDCE913 CDCEL913

IC27 : CDCE913PWR