REL0.1

Page 52 of 95

Kintex Ult FPGA SOM Hardware User Guide

iWave Systems Technologies Pvt. Ltd.

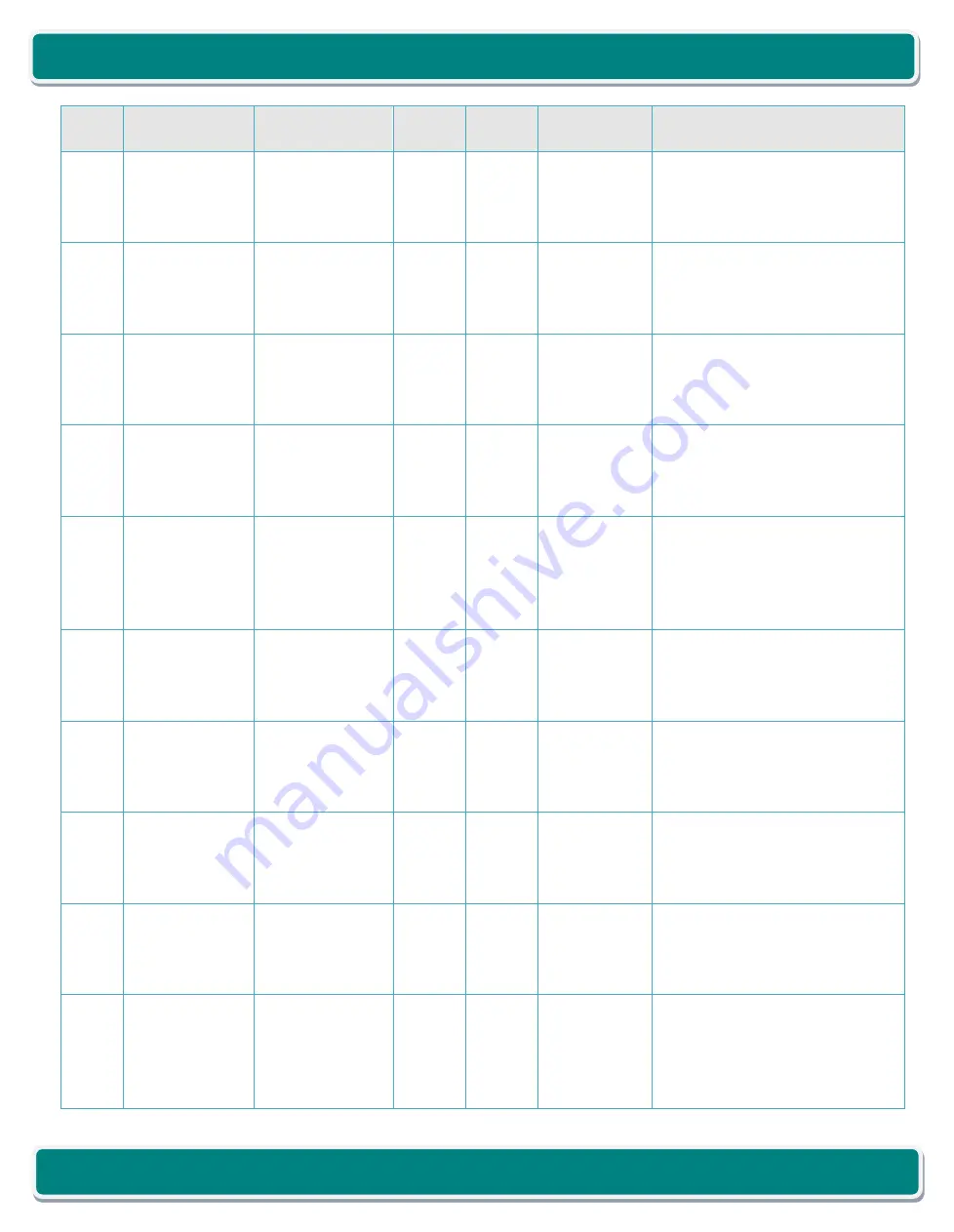

B2B-2

Pin No

B2B Connector2

Signal Name

FPGA Pin Name

FPGA

Bank

FPGA

Pin No

Signal Type/

Termination*

Description

169

PL_AT20_LVDS66

_L14P_GC

IO_L14P_T2L_N2_

GC_66

66

AT20

IO, 1.8V

Bank68 IO14 differential positive

Same pin can be configured as GC

Global Clock Input differential

positive or Single ended I/O.

171

PL_AU20_LVDS6

6_L14N_GC

IO_L14N_T2L_N3_

GC_66

66

AU20

IO, 1.8V

Bank68 IO14 differential negative.

Same pin can be configured as GC

Global Clock Input differential

negative or Single ended I/O.

175

PL_AT19_LVDS66

_L13P_GC

IO_L13P_T2L_N0_

GC_QBC_66

66

AT19

IO, 1.8V

Bank68 IO13 differential positive

Same pin can be configured as GC

Global Clock Input differential

positive or Single ended I/O.

177

PL_AU19_LVDS6

6_L13N_GC

IO_L13N_T2L_N1_

GC_QBC_66

66

AU19

IO, 1.8V

Bank68 IO13 differential negative.

Same pin can be configured as GC

Global Clock Input differential

negative or Single ended I/O.

181

PL_BC17_LVDS66

_L5N

IO_L5N_T0U_N9_

AD14N_66

66

BC17

IO, 1.8V

Bank66 IO5 differential negative.

Same pin can be configured as

PLSYSMON

differential

analog

input14 negative or Single ended

I/O.

183

PL_BB17_LVDS66

_L5P

IO_L5P_T0U_N8_

AD14P_66

66

BB17

IO, 1.8V

Bank66 IO5 differential positive.

Same pin can be configured as

PLSYSMON

differential

analog

input6 positive or Single ended I/O.

122

PL_AN18_LVDS6

6_L19P_DBC

IO_L19P_T3L_N0_

DBC_AD9P_66

66

AN18

IO, 1.8V

Bank66 IO19 differential positive.

Same pin can be configured as

PLSYSMON

differential

analog

input9 positive or Single ended I/O.

124

PL_AN17_LVDS6

6_L19N_DBC

IO_L19N_T3L_N1_

DBC_AD9N_66

66

AN17

IO, 1.8V

Bank66 IO19 differential negative.

Same pin can be configured as

PLSYSMON

differential

analog

input9 negative or Single ended I/O.

126

PL_AW20_LVDS6

6_L9P

IO_L9P_T1L_N4_A

D12P_66

66

AW20

IO, 1.8V

Bank66 IO9 differential positive.

Same pin can be configured as

PLSYSMON

differential

analog

input12 positive or Single ended I/O.

128

PL_AY20_LVDS66

_L9N

IO_L9N_T1L_N5_A

D12N_66

66

AY20

IO, 1.8V

Bank66 IO9 differential negative.

Same pin can be configured as

PLSYSMON

differential

analog

input12 negative or Single ended

I/O.