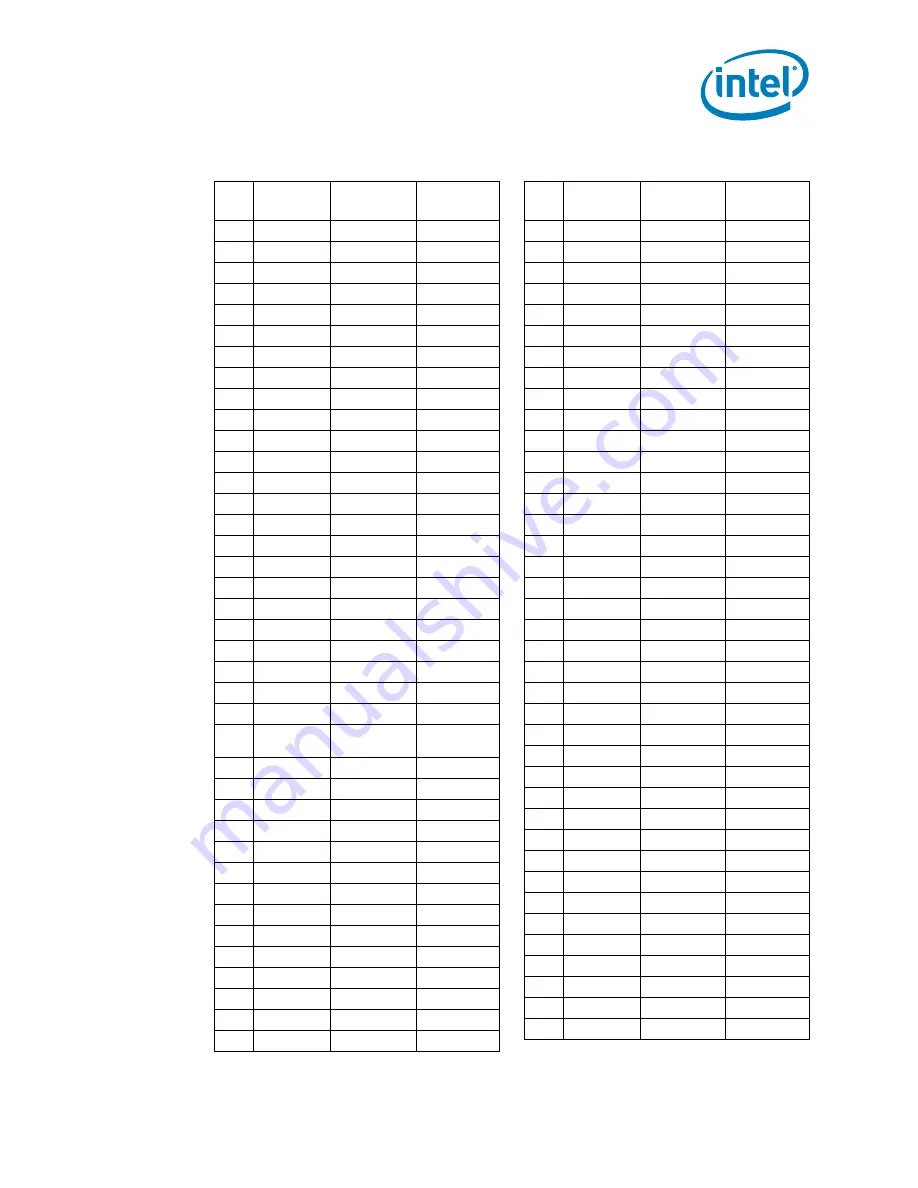

Land Listing and Signal Descriptions

Datasheet

61

H15

FC32

Power/Other

H16

FC33

Power/Other

H17

VSS

Power/Other

H18

VSS

Power/Other

H19

VSS

Power/Other

H2

GTLREF1

Power/Other

Input

H20

VSS

Power/Other

H21

VSS

Power/Other

H22

VSS

Power/Other

H23

VSS

Power/Other

H24

VSS

Power/Other

H25

VSS

Power/Other

H26

VSS

Power/Other

H27

VSS

Power/Other

H28

VSS

Power/Other

H29

FC15

Power/Other

H3

VSS

Power/Other

H30

BSEL1

Asynch CMOS

Output

H4

FC35

Power/Other

H5

TESTHI10

Power/Other

Input

H6

VSS

Power/Other

H7

VSS

Power/Other

H8

VSS

Power/Other

H9

VSS

Power/Other

J1

VTT_OUT_LE

FT

Power/Other

Output

J10

VCC

Power/Other

J11

VCC

Power/Other

J12

VCC

Power/Other

J13

VCC

Power/Other

J14

VCC

Power/Other

J15

VCC

Power/Other

J16

FC31

Power/Other

J17

FC34

Power/Other

J18

VCC

Power/Other

J19

VCC

Power/Other

J2

FC3

Power/Other

J20

VCC

Power/Other

J21

VCC

Power/Other

J22

VCC

Power/Other

Table 4-2.

Numerical Land

Assignment

Land

#

Land Name Signal Buffer

Type

Direction

J23

VCC

Power/Other

J24

VCC

Power/Other

J25

VCC

Power/Other

J26

VCC

Power/Other

J27

VCC

Power/Other

J28

VCC

Power/Other

J29

VCC

Power/Other

J3

FC22

Power/Other

J30

VCC

Power/Other

J4

VSS

Power/Other

J5

REQ1#

Source Synch

Input/Output

J6

REQ4#

Source Synch

Input/Output

J7

VSS

Power/Other

J8

VCC

Power/Other

J9

VCC

Power/Other

K1

LINT0

Asynch CMOS

Input

K2

VSS

Power/Other

K23

VCC

Power/Other

K24

VCC

Power/Other

K25

VCC

Power/Other

K26

VCC

Power/Other

K27

VCC

Power/Other

K28

VCC

Power/Other

K29

VCC

Power/Other

K3

A20M#

Asynch CMOS

Input

K30

VCC

Power/Other

K4

REQ0#

Source Synch

Input/Output

K5

VSS

Power/Other

K6

REQ3#

Source Synch

Input/Output

K7

VSS

Power/Other

K8

VCC

Power/Other

L1

LINT1

Asynch CMOS

Input

L2

TESTHI13

Power/Other

Input

L23

VSS

Power/Other

L24

VSS

Power/Other

L25

VSS

Power/Other

L26

VSS

Power/Other

L27

VSS

Power/Other

L28

VSS

Power/Other

Table 4-2.

Numerical Land

Assignment

Land

#

Land Name Signal Buffer

Type

Direction