MUX/DMUX

The

RIRO

buffer

comprises

total

of

34

guaranteed

and

best

effort

first-in

first-out

FIFO

cell

queues

32

FJFO

queues

for

Line

buffer

guaranteed

IBGO/input

buffer

best

effort

IBBO

through

Line

15

IBG15/IBB15

and two

FIFO

queues

for multicast

buffer

guaranteed

multicast

IBGM/input

buffer

best

effort

multicast

IBBM

The

MUX

multiplexes

cells

from two

lines

and

temporarily

stores

multiplexed

cells

in

the

corresponding

FIFO

queue

The

first

cell

of each

FIFO

queue

is

output

when

back

pressure

BP

is

not received

from

the destination

line

From

IBGMIBBM

however

the

first

cell

is

output

when BP

is

not

received

from

all

lines

The

cells

in

guaranteed

FIFO

queues

are

served

before

those

in

best

effort

queues

Table

B-l

provides

the conditions

in

which

these

four

FIFO

types

are

served

When

the

number

of

cells

stored

in

each

guaranteed

or best

effort

FIFO

queue

exceeds

threshold

or

when

the

number

of

cells

stored

in

an

idle

queue

goes

below

threshold

the system

discards

low-priority

cells

without

saving

them

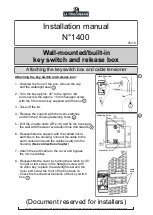

Figure

B-2 shows

the

MUXIDMUX

card

block

diagram

Figure

B-i

ATOMSW

Block

Diagram

LINFO

LINF1

LINF14

LINF15

CTL

ATOM

SW

Asynchronous

transfer

mode

Output-buffer

modular

switch

CTL

Control

DMUX

Demultiplexer

LINF

Line

interface

MUX

Multiplexer

Co

01

B-2

Cisco HyperSwitch

A100

User

Guide