HL-6050/6050D/6050DN SERVICE MANUAL

3-3

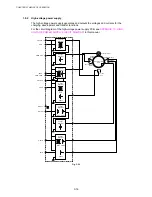

1.3 Main

PCB

For the entire circuit diagram of the main PCB, see

APPENDIX 1. to 6. ‘MAIN PCB CIRCUIT

DIAGRAM’

in this manual.

1.3.1 CPU

A Fujitsu 32bit RISC CPU, SPARClite is built in the ASIC. While the CPU is driven with a

clock frequency of 66.66 MHz in the user logic block, it itself runs at 200 MHz, which is

generated by multiplying the source clock by three.

ADR[2]

ADR[3]

ADR[4]

ADR[5]

ADR[6]

ADR[7]

ADR[8]

ADR[11]

ADR[12]

ADR[13]

ADR[14]

ADR[15]

ADR[16]

ADR[17]

ADR[18]

ADR[19]

ADR[20]

ADR[21]

ADR[22]

ADR[23]

DATA[0]

DATA[1]

DATA[2]

DATA[3]

DATA[4]

ADR[1]

DATA[5]

DATA[6]

DATA[7]

DATA[8]

DATA[9]

DATA[10]

DATA[11]

DATA[12]

DATA[13]

DATA[14]

DATA[15]

ADR[10]

ADR[9]

R159

33

R160

33

R169

33

R171

33

R79

51

R80

0

R83

0

R76

51

R70

51

R69

33

R72

33

R74

33

R71

33

4-3C/4-5D

ROMCSN0

4-2C

ROMCSN1

4-2C/4-3C/4-7C/6-2E

IOWEN

4-2C/4-3C/4-5D/4-7C/6-2E

IORDN

4-1A

SDCLK0

3-3C

SDCLK1

3-3C

SDCLK2

4-1A

SDCKE0

4-1A

SDCSN0

3-1C

SDCSN1

3-1C

SDCSN2

3-1C

SDSDA

3-1C

SDSCL

3-1E/3-3C/3-4D/

4-1C/4-1E/4-6B/

4-1A/3-1D

ADR[23-1]

3-4A/3-4B/4-2F

DATA[15-0]

U5

CY25814

XIN

1

XOUT

8

FRSEL

6

S1

3

S0

4

SSCLK

5

VDD

7

VSS

2

VDD3

0V

C62

C103

0V

C63

22PF

C64

18PF

R82

0

R81

0

VDD3

R96

1M

R95

1k

R98

0

R97

0

R73

4.7k

VDD3

3-3B

SDCKE1

R172

68

C138

C101

0V

R42

10k

R47

10k

R67

10k

R66

10k

R65

10k

R94

10k

R68

10k

R48

10k

R43

10k

R92

10k

R93

10k

R45

10k

R46

10k

R44

10k

R49

10k

VDD3

0V

0V

TP247

TP73

TP72

TP195

TP243

TP245

TP260

TP263

TP96

TP98

TP100

TP93

R78

0

TP99

TP102

TP97

TP95

TP94

TP101

TP74

TP71

TP69

R64

10k

R41

10k

R39

10k

TP244

TP246

TP262

TP261

TP75

R40

10k

R77

4.7k

R75

4.7k

0V

TP70

TP154

TP153

TP157

TP259

4-7C

LAN_CSN

4-7D

LAN_DACKN

4-7D

LAN_INTN

4-7D

LAN_DREQN

4-7D

LAN_READYN

R104

33

R102

33

U8

Aurora

DATA00

40

DATA01

41

DATA02

42

DATA03

43

DATA04

44

DATA05

45

DATA06

46

DATA07

47

DATA08

48

DATA09

49

DATA10

53

DATA11

54

DATA12

55

DATA13

56

DATA14

57

DATA15

58

DATA16/IO

59

DATA17/IO

60

DATA18/IO

61

DATA19/IO

62

DATA20/IO

63

DATA21/IO

64

DATA22/IO

67

DATA23/IO

68

DATA24/IO

69

DATA25/IO

70

DATA26/IO

71

DATA27/IO

72

DATA28/IO

73

DATA29/IO

74

DATA30/IO

75

DATA31/IO

76

EXINTN0

196

RSTN

216

SCKOUT

87

SCKIN

85

ADR01/24

9

ADR02

10

ADR03

11

ADR04

12

ADR05

13

ADR06

14

ADR07

15

ADR08

16

ADR09

17

ADR10

18

ADR11

19

ADR12

25

ADR13

26

ADR14

27

ADR15/BA0

28

ADR16/BA1

29

ADR17/RASN

30

ADR18/CASN

31

ADR19/WEN

32

ADR20/DQM0

33

ADR21/DQM1

34

ADR22/DQM2

35

ADR23/DQM3

36

ROMCSN0

211

ROMCSN1

212

IOWEN

213

IORDN

214

SDCLK0

95

SDCLK1

94

SDCLK2

93

SDCKE0

96

SDCKE1

97

SDCSN0

90

SDCSN1

89

SDCSN2

88

SDSDA

92

SDSCL

91

C137

C103

U13

R3112N281C

5

CD

2

VCC

1

VOUT

4

NC

3

GND

TP258

VDD3

C136

C103

0V

L33

(1608)0.68

C65

C103

TP76

TP111

TP107

R163

33

TP194

TP196

TP197

TP152

6-2E

MED_CSN

2-6D

PREREG

R126

33

R125

33

TP159

TP158

TP117

X1

AT-49 16.6666MHZ

1

2

5F

SLEEP

2-2E

DEVVER

6-2D MED_INTN

4D

SENON/OFF

R105

33

TP112

TP108

TP110

R101

0

0V

TP105

TP151

2-2E

REARTRAY

7E

COVER

0V

R103

0

R106

0

TP113

TP109

TP160

TP116

R250

10k

R251

10k

Fig. 3-3