Chapter 1: Product Introduction

1-16

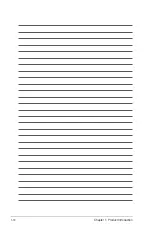

Action

PHASE

POST CODE

TYPE

DESCRIPTION

PSP Boot

PSP Boot Loader

phase (Status Post

Codes)

0xA0

Progress

Bootloader successfully entered C Main

0xA1

Progress

Master initialized C2P / slave waited for master to init C2P

0xA2

Progress

HMAC key successfully derived

0xA3

Progress

Master got Boot Mode and sent boot mode to all slaves

0xA4

Progress

SpiRom successfully initialized

0xA5

Progress

BIOS Directory successfully read from SPI to SRAM

0xA6

Progress

Early unlock check

0xA7

Progress

Inline Aes key successfully derived

0xA8

Progress

Inline-AES key programming is done

0xA9

Progress

Inline-AES key wrapper derivation is done

0xAA

Progress

Bootloader successfully loaded HW IP configuration values

0xAB

Progress

Bootloader successfully programmed MBAT table

0xAC

Progress

Bootloader successfully loaded SMU FW

0xAD

Progress

PSP and SMU configured WAFL

0xAE

Progress

User mode test harness completed successfully

0xAF

Progress

Bootloader loaded Agesa0 from SpiRom

0xB0

Progress

AGESA phase has completed

0xB1

Progress

RunPostDramTrainingTests() completed successfully

0xB2

Progress

SMU FW Successfully loaded to SMU Secure DRAM

0xB3

Progress

Sent all required boot time messages to SMU

0xB4

Progress

Validated and ran Security Gasket binary

0xB5

Progress

UMC Keys generated and programmed

0xB6

Progress

Inline AES key wrapper stored in DRAM

0xB7

Progress

Completed FW Validation step

0xB8

Progress

Completed FW Validation step

0xB9

Progress

BIOS copy from SPI to DRAM complete

0xBA

Progress

Completed FW Validation step

0xBB

Progress

BIOS load process fully complete

0xBC

Progress

Bootloader successfully release x86

0xBD

Progress

Early Secure Debug completed

0xBE

Progress

GetFWVersion command received from BIOS is completed

0xBF

Progress

SMIInfo command received from BIOS is completed

0xC0

Progress

Successfully entered WarmBootResume()

0xC1

Progress

Successfully copied SecureOS image to SRAM

0xC2

Progress

Successfully copied trustlets to PSP Secure Memory

0xC3

Progress

About to jump to Secure OS (SBL about to copy and jump)

0xC4

Progress

Successfully restored CCP and UMC state on S3 resume

0xC5

Progress

PSP SRAM HMAC validated by Mini BL

0xC6

Progress

About to jump to <t-base in Mini BL

0xC7

Progress

VMG ECDH unit test started

0xC8

Progress

VMG ECDH unit test passed

0xC9

Progress

VMG ECC CDH primitive unit test started

0xCA

Progress

VMG ECC CDH primitive unit test passed

0xCB

Progress

VMG SP800-108 KDF-CTR HMAC unit test started

0xCC

Progress

VMG SP800-108 KDF-CTR HMAC unit test passed

0xCD

Progress

VMG LAUNCH_* test started

0xCE

Progress

VMG LAUNCH_* test passed

0xCF

Progress

MP1 has been taken out of reset

0xD0

Progress

PSP and SMU Reserved Addresses correct

0xD1

Progress

Reached Naples steady-state WFI loop

0xD2

Progress

Knoll device successfully initialized

0xD3

Progress

32-byte RandOut successfully returned from Knoll

0xD4

Progress

32-byte MAC successfully received from Knoll.

0xD5

Progress

Knoll device verified successfully

0xD6

Progress

Done enabling power for Knoll

0xD7

Progress

Enter recovery mode due to trustlet validation fail.

0xD8

Progress

Enter recovery mode due to OS validation fail.

0xD9

Progress

Enter recovery mode due to OEM public key not found.

(continued on the next page)

Summary of Contents for RS720-E9-RS8

Page 1: ...2U Rackmount Server User Guide RS720 E9 RS8 RS8 G ...

Page 28: ...Chapter 1 Product Introduction 1 18 ...

Page 84: ...Chapter 2 Hardware Information 2 56 ...

Page 90: ...Chapter 3 Installation Options 3 6 3 3 Rail kit dimensions 589mm 43 6mm 900mm 43 6mm ...

Page 92: ...Chapter 4 Motherboard Information 4 2 4 1 Motherboard layout ...

Page 116: ...Chapter 4 Motherboard Information 4 26 ...

Page 158: ...5 42 Chapter 5 BIOS Setup ...

Page 200: ...A 8 Appendix ...