ADVANCED CHIPSET SETUP Options,

Continued

On Board Serial Port 2

This option enables or disables serial port 2 on the Mark V motherboard. The settings are I/O Ports

2F8h

- 2FFh,

2E8h

- 2EFh,

or

Disabled

.

If the configuration data stored in CMOS RAM is corrupted when the system is powered on, AMIBIOS automatically configures

onboard serial port 2 according to the presence or absence of serial ports on adapter cards in the expansion slots (offboard

serial ports). Autoconfiguration only occurs when CMOS RAM data is corrupted. The result for serial port 2 is:

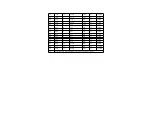

If the Offboard

Serial Port is

the Onboard Serial Port 2 is Autoconfigured as

None

2F8h

Can be disabled or changed to 2E8h via ADVANCED

CHIPSET SETUP.

2F8h

2E8h

Can be disabled via ADVANCED CHIPSET SETUP. If

changed to 2F8h, an I/O port address conflict occurs.

2E8h

2F8h

Can be disabled via ADVANCED CHIPSET SETUP. If

changed to 2E8h, an I/O port address conflict occurs.

2F8h, 2E8h

Disabled

If changed to 3F8h or 3E8h, an I/O port address

conflict occurs.

P1 is serial port 2 on the Mark V Baby Screamer motherboard. If disabled through Setup, do not attach any device to P1 or to

any cable attached to P1. J21 is used to configure the interrupt request line (IRQ) for onboard serial port 2. The J21 settings

are:

Jumper

Pins Shorted

Description

J21

Pins 1-2

IRQ4 selected for onboard serial port 2.

J21

Pins 2-3

IRQ3 selected for onboard serial port 2 (Default).

If onboard serial sort 2 is disabled, you can remove the jumper block from J21 to disable the onboard serial port 2 interrupt.

Summary of Contents for 42 Series

Page 1: ...American Megatrends Inc Series 42 Mark V Baby Screamer 80386 Motherboard User s Guide ...

Page 2: ...MAN 642 Rev C 9 11 92 ...

Page 13: ......

Page 35: ...A29 SA02 B29 5 A30 SA01 B30 OSC A31 SA00 B31 GND ...

Page 59: ......

Page 82: ......

Page 85: ...SRAM Locations ...