Z8018x

Family MPU User Manual

UM005004-0918

71

stacked PC-1. If UFO is

1

, the starting address of the invalid instruction is

equal to the stacked PC-2.

Bus Release cycle, Refresh cycle, DMA cycle, and WAIT cycle cannot be

inserted just after TTP state which is inserted for TRAP interrupt

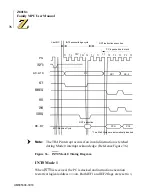

sequence. Figure depicts TRAP Timing - 2nd Op Code undefined and

Figure illustrates Trap Timing - 3rd Op Code undefined.

Figure 32. TRAP Timing Diagram -2nd Op Code Undefined

2nd Op Code

Fetch Cycle

PC Stacking

Restart from 0000H

Op Code

Fetch Cycle

PC

SP-1

SP-2

0000H

Undefined

Op Code

Ti

Ti

Ti

T1

Ti

Ti

T1

T2

T3

T2

T3 T1

T2

T3

T1

T2

T3

Phi

A0

–

A19

WR

RD

MREQ

D0

–

D7

MI

PCH

PCL

Содержание Z8018 Series

Страница 1: ...www zilog com Z8018x Family MPU User Manual UM005004 0918...

Страница 206: ...Z8018x Family MPU User Manual 192 UM005004 0918...

Страница 220: ...Z8018x Family MPU User Manual 206 UM005004 0918...

Страница 250: ...Z8018x Family MPU User Manual 236 UM005004 0918...

Страница 260: ...Z8018x Family MPU User Manual 246 UM005004 0918...

Страница 300: ...Z8018x Family MPU User Manual 286 UM005004 0918...

Страница 306: ...Z8018x Family MPU User Manual 292 UM005004 0918...