Z8018x

Family MPU User Manual

72

UM005004-0918

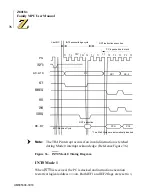

Figure 33. TRAP Timing - 3rd Op Code Undefined

External Interrupts

The Z8X180 features four external hardware interrupt inputs:

•

NMI–Non-maskable interrupt

•

INT0–Maskable Interrupt Level 0

•

INT1–Maskable Interrupt Level 1

•

INT2–Maskable Interrupt Level 2

NMI, INT1, and INT2 feature fixed interrupt response modes. INT0 has 3

different software programmable interrupt response modes—Mode 0,

Mode 1 and Mode 2.

NMI - Non-Maskable Interrupt

The

NMI

interrupt input is edge-sensitive and cannot be masked by

software. When

NMI

is detected, the Z8X180 operates as follows:

Phi

A0

–

A19

WR

RD

MREQ

D0

–

D7

MI

Ti

T1

Ti

Ti

T1 T2 T3

T2

T3

T1

T3

T1 T2

T3

T1 T2 TTP

T1 T2 T3

Memory

PC stacking

Restart from 0000H

Op Code

fetch cycle

0000H

SP-1

SP-2

PCL

PCH

IX+d, IY+d

PC

3rd Op Code

Fetch Cycle

Undefined

Op Code

Read Cycle

Содержание Z8018 Series

Страница 1: ...www zilog com Z8018x Family MPU User Manual UM005004 0918...

Страница 206: ...Z8018x Family MPU User Manual 192 UM005004 0918...

Страница 220: ...Z8018x Family MPU User Manual 206 UM005004 0918...

Страница 250: ...Z8018x Family MPU User Manual 236 UM005004 0918...

Страница 260: ...Z8018x Family MPU User Manual 246 UM005004 0918...

Страница 300: ...Z8018x Family MPU User Manual 286 UM005004 0918...

Страница 306: ...Z8018x Family MPU User Manual 292 UM005004 0918...