Z8018x

Family MPU User Manual

62

UM005004-0918

MMU Bank Base Register (BBR)

BBR specifies the base address (on 4KB boundaries) used to generate a

20-bit physical address for Bank Area accesses. All bits of BBR are reset

to

0

during RESET.

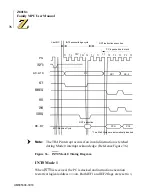

Physical Address Translation

Figure 29 illustrates the way in which physical addresses are generated

based on the contents of CBAR, CBR and BBR. MMU comparators

classify an access by logical area as defined by CBAR. Depending on

which of the three potential logical areas (Common Area 1, Bank Area, or

Common Area 0) is being accessed, the appropriate 8- or 7-bit base

address is added to the high-order 4 bits of the logical address, yielding a

19- or 20-bit physical address. CBR is associated with Common Area 1

accesses. Common Area 0, if defined, is always based at physical address

00000H

.

MMU Bank Base Register (BBR: 39H)

Bit

7

6

5

4

3

2

1

0

Bit/Field

BB7

BB6

BB5

BB4

BB3

BB2

BB1

BB0

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

Reset

0

0

0

0

0

0

0

0

Note: R = Read W = Write X = Indeterminate ? = Not Applicable

Bit

Position

Bit/Field

R/W

Value Description

7

–

0

BB7

–

0

R/W

BBR specifies the base address (on 4KB boundaries) used

to generate a 20-bit physical address for Bank Area

accesses.

Содержание Z8018 Series

Страница 1: ...www zilog com Z8018x Family MPU User Manual UM005004 0918...

Страница 206: ...Z8018x Family MPU User Manual 192 UM005004 0918...

Страница 220: ...Z8018x Family MPU User Manual 206 UM005004 0918...

Страница 250: ...Z8018x Family MPU User Manual 236 UM005004 0918...

Страница 260: ...Z8018x Family MPU User Manual 246 UM005004 0918...

Страница 300: ...Z8018x Family MPU User Manual 286 UM005004 0918...

Страница 306: ...Z8018x Family MPU User Manual 292 UM005004 0918...