16

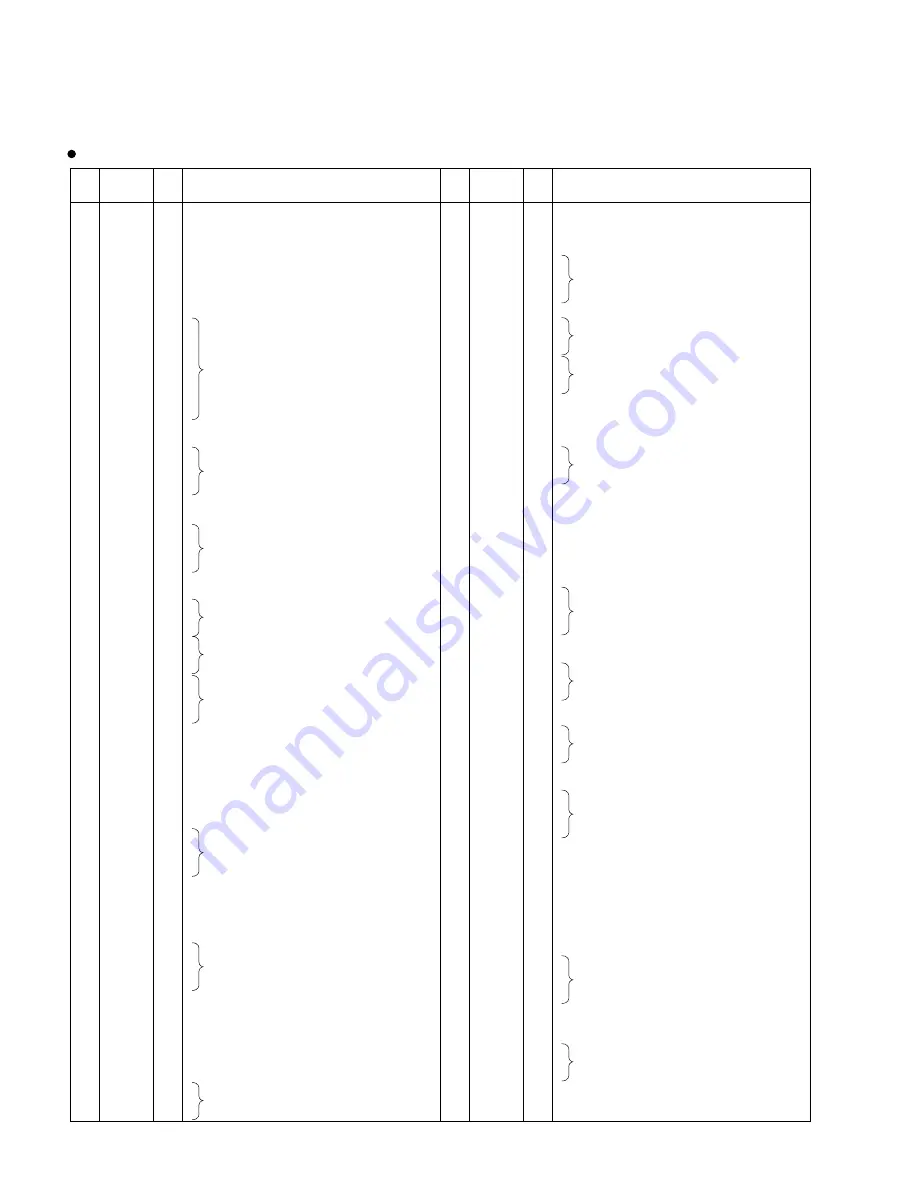

AD8HR

PIN

NO.

I/O

FUNCTION

NAME

PIN

NO.

I/O

FUNCTION

NAME

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

33

34

35

36

37

38

39

40

41

42

43

44

45

46

47

48

49

50

51

52

53

54

55

56

57

58

59

60

61

62

63

64

65

66

67

68

69

70

71

72

V

DD

XTST

V

SS

WT_X

RD_X

CS_X

HS_SEL

RES_X

V

SS

ADD[0]

ADD[1]

ADD[2]

ADD[3]

ADD[4]

ADD[5]

ADD[6]

ADD[7]

V

DD

V

SS

DAT[0]

DAT[1]

DAT[2]

DAT[3]

V

DD

V

SS

DAT[4]

DAT[5]

DAT[6]

DAT[7]

V

SS

V

DD

PA_I_H_MODE[0]

PA_I_H_MODE[1]

PA_I_H_MODE[2]

PA_O_H_MODE[0]

PA_O_H_MODE[1]

PA_O_H_MODE[2]

PA_SI0_ATI

PA_SI1

PA_SI2

PA_SI3

PA_I_SW_SEL

PA_SYNC_WC_SI

PA_FS256_SI

V

SS

PA_FS256_SO

PA_SYNC_WC_SO

PA_O_SW_SEL

V

SS

PA_SO0

PA_SO1

PA_SO2

PA_SO3

V

DD

V

SS

PA_CLK_ATI

PA_H_M4_SEL

PA_O_MUTE

PB_SI0

PB_SI1

PB_SI2

PB_SI3

PB_I_SW_SEL

PB_SYNC_WC_SI

PB_FS256_SI

V

SS

PB_FS256_SO

PB_SYNC_WC_SO

PB_O_SW_SEL

PB_I_H_MODE[0]

PB_I_H_MODE[1]

PB_I_H_MODE[2]

I

I

I

I

I

I

I

I

I

I

I

I

I

I

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I

I

I

I

I

I

I

I

I

I

I

I

I

I

I

I

O

O

O

O

I

I

I

I

I

I

I

I

I

I

I

I

I

I

I

I

Power 3.3V

LSI test pin

Ground

CPU interface write input

CPU interface read input

CPU interface chip select input

Chip active select

System reset input

Ground

CPU interface address bus

Power 3.3V

Ground

CPU interface data bus

Power 3.3V

Ground

CPU interface data bus

Ground

Power 3.3V

Port A audio data input mode select

Port A audio data output mode select

Port A audio data input

Port A audio data input sync/wc select

Port A audio data input sync/wc input

Port A audio data input bit clock input (256fs)

Ground

Port A audio data output bit clock input (256fs)

Port A audio data output sync/wc input

Port A audio data output sync/wc select

Ground

Port A audio data output

Power 3.3V

Ground

Port A ADAT clock input

Port A audio data input buffer active select

Port A mute

Port B audio data input

Port B audio data input sync/wc select

Port B audio data input sync/wc input

Port B audio data input bit clock input (256fs)

Ground

Port B audio data output bit clock input (256fs)

Port B audio data output sync/wc input

Port B audio data output sync/wc select

Port B audio data input mode select

73

74

75

76

77

78

79

80

81

82

83

84

85

86

87

88

89

90

91

92

93

94

95

96

97

98

99

100

101

102

103

104

105

106

107

108

109

110

111

112

113

114

115

116

117

118

119

120

121

122

123

124

125

126

127

128

129

130

131

132

133

134

135

136

137

138

139

140

141

142

143

144

V

DD

PB_H_M4_SEL

PB_O_MUTE

V

SS

PB_SO0_ATO

PB_SO1

PB_SO2

PB_SO3

V

SS

PB_O_H_MODE[0]

PB_O_H_MODE[1]

PB_O_H_MODE[2]

PC_I_H_MODE[0]

PC_I_H_MODE[1]

PC_I_H_MODE[2]

PC_H_M4_SEL

PC_SI0_ATI

V

DD

V

SS

PC_SI1

PC_SI2

PC_SI3

PC_I_SW_SEL

PC_SYNC_WC_SI

PC_FS256_SI

V

SS

PC_FS256_SO

PC_SYNC_WC_SO

PC_O_SW_SEL

V

SS

PC_SO0

PC_SO1

PC_SO2

PC_SO3

V

SS

PC_O_MUTE

PC_O_H_MODE[0]

PC_O_H_MODE[1]

PC_O_H_MODE[2]

PC_CLK_ATI

V

SS

PD_I_H_MODE[0]

PD_I_H_MODE[1]

PD_I_H_MODE[2]

V

SS

PD_H_M4_SEL

PD_SI0

PD_SI1

PD_SI2

PD_SI3

PD_I_SW_SEL

PD_SYNC_WC_SI

PD_FS256_SI

V

DD

V

SS

PD_FS256_SO

PD_SYNC_WC_SO

PD_O_SW_SEL

V

SS

PD_SO0_ATO

PD_SO1

PD_SO2

PD_SO3

V

SS

PD_O_MUTE

V

SS

PD_O_H_MODE[0]

PD_O_H_MODE[1]

PD_O_H_MODE[2]

XSM

PA_WC_ATI

PC_WC_ATI

I

I

O

O

O

O

I

I

I

I

I

I

I

I

I

I

I

I

I

I

I

I

I

O

O

O

O

I

I

I

I

I

I

I

I

I

I

I

I

I

I

I

I

I

I

I

O

O

O

O

I

I

I

I

I

O

O

Power 3.3V

Port B audio data input buffer active select

Port B mute

Ground

Port B audio data output

Ground

Port B audio data output mode select

Port C audio data input mode select

Port C audio data input buffer active select

Port C audio data input

Power 3.3V

Ground

Port C audio data input

Port C audio data input sync/wc select

Port C audio data input sync/wc input

Port C audio data input bit clock input (256fs)

Ground

Port C audio data output bit clock input (256fs)

Port C audio data output sync/wc input

Port C audio data output sync/wc select

Ground

Port C audio data output

Ground

Port C mute

Port C audio data output mode select

Port C ADAT clock input

Ground

Port D audio data input mode select

Ground

Port D audio data input buffer active select

Port D audio data input

Port D audio data input sync/wc select

Port D audio data input sync/wc input

Port D audio data input bit clock input (256fs)

Power 3.3V

Ground

Port D audio data output bit clock input (256fs)

Port D audio data output sync/wc input

Port D audio data output sync/wc select

Ground

Port D audio data output

Ground

Port D mute

Ground

Port D audio data output mode select

LSI test pin

Port A ADAT word clock output

Port C ADAT word clock output

MBCG61594-130 (X3299A00) ATSC2A

MAIN: IC921

Содержание AD8HR

Страница 8: ...8 AD8HR CIRCUIT BOARD LAYOUT DC MAIN COMB SW SUB PN PNCOM PNCOM PNCOM PNCOM PNCOM HIC HA ユニットレイアウト ...

Страница 24: ...24 AD8HR MAIN Circuit Board B B 2NAP WC06220 D010 1 ...

Страница 25: ...AD8HR 25 B B Shield MAIN Soldering ハンダ付け シールドMAIN Pattern side 2NAP WC06220 D010 1 パターン側 ...

Страница 26: ...26 AD8HR C C 1 2 3 4 5 6 D D PN Circuit Board E E to MAIN CN982 F F DC Circuit Board 2NAP WC06230 D010 1 ...