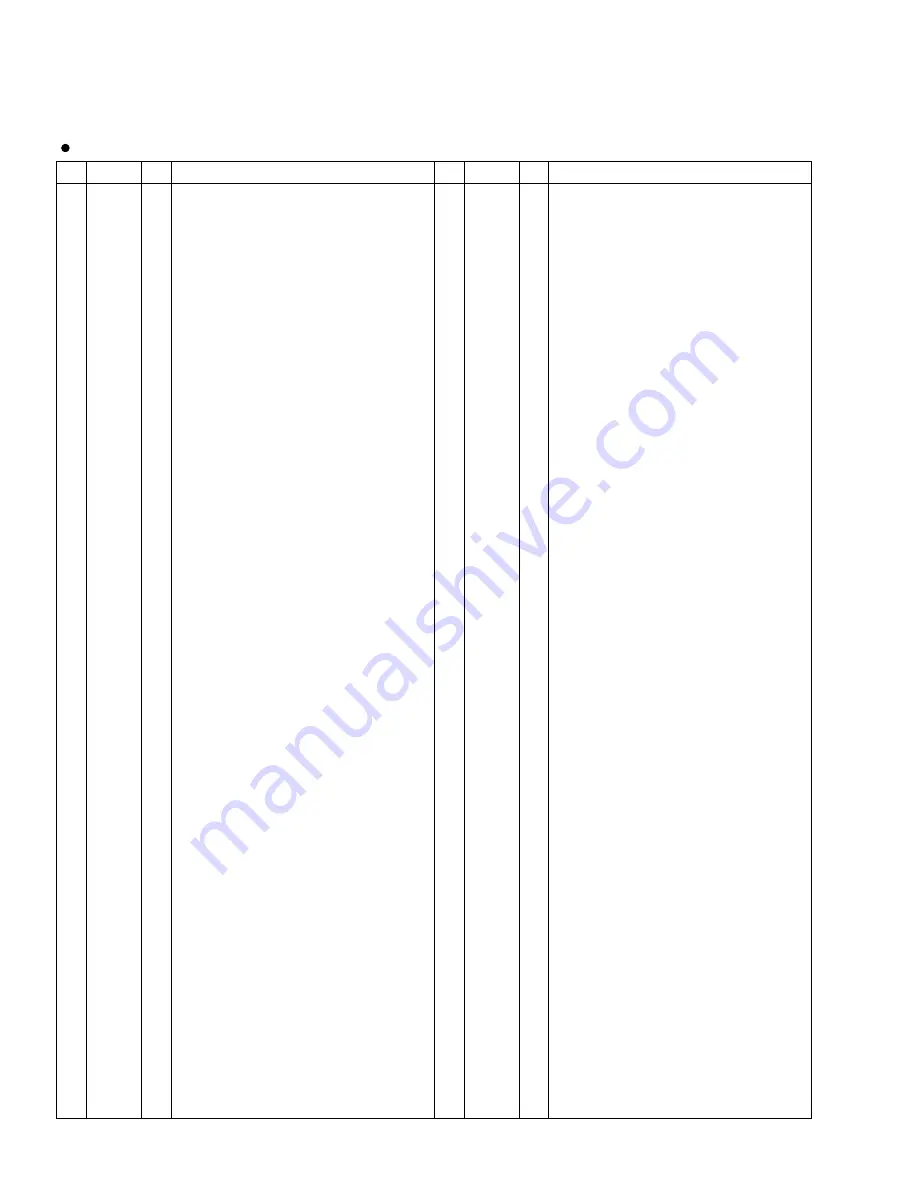

14

AD8HR

PIN

NO.

I/O

FUNCTION

NAME

PIN

NO.

I/O

FUNCTION

NAME

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

33

34

35

36

37

38

39

40

41

42

43

44

45

46

47

48

49

50

51

52

53

54

55

56

57

58

59

60

61

62

63

64

65

66

67

68

69

70

71

72

73

74

75

76

77

78

79

80

81

82

83

84

85

86

87

88

89

90

91

92

93

94

95

96

97

98

99

100

101

102

103

104

-

-

O

O

-

-

O

I

I

I

I

I

O

I

I

I

I

I

O

-

-

-

-

I

I

I

I

I

I

I

I

-

-

-

-

I/O

I/O

I/O

I/O

I/O

I/O

-

-

I/O

I/O

I/O

I/O

-

-

-

-

-

I/O

I/O

I/O

I/O

I/O

I/O

-

O

O

O

O

O

O

-

O

O

O

O

O

-

O

O

O

-

-

I

I

-

-

-

O

-

O

O

O

O

O

I

-

O

O

O

O

O

O

-

O

O

O

O

O

O

105

106

107

108

109

110

111

112

113

114

115

116

117

118

119

120

121

122

123

124

125

126

127

128

129

130

131

132

133

134

135

136

137

138

139

140

141

142

143

144

145

146

147

148

149

150

151

152

153

154

155

156

157

158

159

160

161

162

163

164

165

166

167

168

169

170

171

172

173

174

175

176

177

178

179

180

181

182

183

184

185

186

187

188

189

190

191

192

193

194

195

196

197

198

199

200

201

202

203

204

205

206

207

208

(NC)

(NC)

PB8

PB9

VDD

VSS

PA0

NCSIN6

NCSIN5

NRD

NWRH

NWRL

PA1

ADH1

ADH2

ADH3

ADH4

ADH5

PA2

VSS

VDD

VDD

VSS

ADL1

ADL2

ADL3

ADL4

ADL5

ADL6

ADL7

ADL8

VSS

VDD

VDD

VSS

DT0

DT1

DT2

DT3

DT4

DT5

VDD

VSS

DT6

DT7

DT8

DT9

VDD

VSS

(NC)

(NC)

(NC)

DT10

DT11

DT12

DT13

DT14

DT15

VSS

PA3

NTCWAIT

NCSIO3V

NCSIO5V

NCSJK1

NCSCONT

VDD

NCSSLOT1

NCSSLOT2

NCSSIO4

NCSREC2

NCSMTLED

VDD

NCSUSB

NCSSMPTE

NCSUART

VSS

VDD

NRES

CPUCLK

(NC)

VSS

VSS

NCSATSC1

VDD

NCSATSC2

PA4

PA5

PA6

NCTSYNCO

NCTSYNCI

VDD

NCSDSP71

NCSDSP72

NCSDSP73

NCSDSP74

NCSDSP75

NCSDSP76

VDD

PA7

PA8

NCSDSP61

NCSDSP62

NCSDSP63

NCSDSP64

(NC)

VDD

(NC)

(NC)

VSS

VDD

NCSDSP7

NCSDSP6

PA9

MCK256O

MCK256MI

MCK256SI

VSS

VDD

ICK45

ICK49

DIR2XI

PA10

VSS

VDD

EXTWC1

EXTWC2

EXTWC3

EXTWC4

VSS

VDD

EXTWC2561

EXTWC2562

PA11

DIRMCA

DIRMCB

DIRWC

VSS

VDD

DIRMCC

DIRSYNC

EXTWCSEL

DIRWCSEL

PA12

PLLOUT

VSS

VDD

PCPOUT

PA13

M256FS

M128FS

VSS

VDD

(NC)

(NC)

(NC)

(NC)

M64FS

MWC

MSYNC

PA14

WCO_BNC

PA15

FS256_SLOT1

FS256_SLOT2

VDD

SYNC_SLOT1

SYNC_SLOT2

PB0

SLOT_12M

SLOT_6M

VSS

SLOT_3M

PB1

SLOT_48K

SLOT_48S

PB2

ANA256FS

VDD

NLOCK

NDIRLOCK

VSS

SCANEN

ATPGEN

TSTEN

VDD

TRRERR1

TRRERR2

VSS

PB3

NMLOCKSEL

NLOCKRTN

PB4

MUTEIN

VDD

MUTEOUT1

MUTEOUT2

MUTEOUT3

MUTEOUT4

MUTEOUT5

NMUTEOUT6

VDD

PB5

DOUBLE

K48K96

PB6

SLOT1_16CH

SLOT2_16CH

PB7

-

-

-

-

-

-

O

O

O

O

I

I

-

-

I

I

O

O

-

-

I

I

I

I

-

-

I

I

O

I

I

I

-

-

I

I

O

O

O

I

-

-

O

O

O

O

-

-

-

-

-

-

O

O

O

O

O

O

O

O

-

O

O

O

O

O

-

O

O

O

O

O

O

-

I

I

-

I

I

I

-

I

I

-

O

O

I

O

I

-

O

O

O

O

O

O

-

O

O

O

O

O

O

O

(Connected to VSS on P.C.B.)

(Pulled up on P.C.B.)

Output port B8

Output port B9

IO power supply (3.3V)

Ground

Output port A0

CPU chip select 6

CPU chip select 5

CPU read enable

CPU write enable H

CPU write enable L

Output port A1

CPU address bus 11

CPU address bus 12

CPU address bus 13

CPU address bus 14

CPU address bus 15

Output port A2

Ground

Internal power supply (2.5V)

IO power supply (3.3V)

Ground

CPU address bus 1

CPU address bus 2

CPU address bus 3

CPU address bus 4

CPU address bus 5

CPU address bus 6

CPU address bus 7

CPU address bus 8

Ground

Internal power supply (2.5V)

IO power supply (3.3V)

Ground

CPU data bus 0

CPU data bus 1

CPU data bus 2

CPU data bus 3

CPU data bus 4

CPU data bus 5

IO power supply (3.3V)

Ground

CPU data bus 6

CPU data bus 7

CPU data bus 8

CPU data bus 9

Internal power supply (2.5V)

Ground

(Connected to VDD on P.C.B.)

(Connected to VDD on P.C.B.)

(Pulled up on P.C.B.)

CPU data bus 10

CPU data bus 11

CPU data bus 12

CPU data bus 13

CPU data bus 14

CPU data bus 15

Ground

Output port A3

CPU wait signal

Chip select (103V)

Chip select (105V)

Chip select (JK1)

Chip select (CONT)

Power supply

Chip select (SLOT1)

Chip select (SLOT2)

Chip select (S104)

Chip select (REC2)

Chip select (MTLED)

Power supply

Chip select (USB)

Chip select (SMPTE)

Chip select (UART)

Ground

Power supply

System reset

CPU clock

(Connected to VSS on P.C.B.)

Ground

Ground

Chip select (ATSC1)

Power supply

Chip select (ATSC2)

Output port A4

Output port A5

Output port A6

Internal counter synchronous signal output

Internal counter synchronous signal input

Power supply

Chip select (DSP7_1)

Chip select (DSP7_2)

Chip select (DSP7_3)

Chip select (DSP7_4)

Chip select (DSP7_5)

Chip select (DSP7_6)

Power supply

Output port A7

Output port A8

Chip select (DSP6_1)

Chip select (DSP6_2)

Chip select (DSP6_3)

Chip select (DSP6_4)

(Pulled up on P.C.B.)

Power supply

(Connected to VSS on P.C.B.)

(Connected to VSS on P.C.B.)

Ground

Power supply

Chip select (DSP7_ALL)

Chip select (DSP6_ALL)

Output port A9

256FS synchronous clock output

256FS synchronous clock input (Master)

256FS synchronous clock input (Slave)

Ground

Power supply

For internal clock 88.2k, 44.1k

For internal clock 96k, 48k

Clock for X1 of DIR2

Output port A10

Ground

Power supply

External word clock input 1

External word clock input 2

External word clock input 3

External word clock input 4

Ground

Power supply

External WC (256FS) input 1

External WC (256FS) input 2

Output port A11

MCA input of DIR2

MCB input of DIR2

WC input of DIR2

Ground

Power supply

MCC input of DIR2

SYNC input of DIR2

EXTWC clock select output

DIRWC clock select output

Output port A12

PLL VCO OUT input

Ground

Power supply

EXT WC SEL to MWC comparison circuit output

Output port A13

Master clock (256FS)

System clock (128FS)

Ground

Power supply

(Connected to VDD on P.C.B.)

(Connected to VSS on P.C.B.)

(Pulled up on P.C.B.)

(Pulled up on P.C.B.)

System clock (64FS)

Word clock

Synchronous signal

Output port A14

WC output for BNC connector

Output port A15

Clock (256FS) for MY SLOT1

Clock (256FS) for MY SLOT2

Power supply

Synchronous signal for MY SLOT1

Synchronous signal for MY SLOT2

Output port 80

Clock (12MHz) for MY SLOT

Clock (6MHz) for MY SLOT

Ground

Clock (3MHz) for MY SLOT

Output port B1

Word clock (48/44) for MY SLOT

Synchronous signal (48/44) for MY SLOT

Output port B2

Clock for analog circuit

Power supply

PLL lock detect signal

DIR2 PLL lock signal

Ground

Scan test input

ATPG test input

Test mode selection

Power supply

2TR DIN UNLOCK input

2TR DIN UNLOCK input

Ground

Output port B3

Lock select output

Lock delay input

Output port B4

Mute input

Power supply

Mute output 1

Mute output 2

Mute output 3

Mute output 4

Mute output 5

Mute output 6

Power supply

Output port B5

Register setting value output

Register setting value output

Output port B6

SLOT1 16/8 ch selection

SLOT2 16/8 ch selection

Output port B7

S1L51252F32S000 (X3775A00) PLLP2 (Gate Array)

MAIN: IC52

Содержание AD8HR

Страница 8: ...8 AD8HR CIRCUIT BOARD LAYOUT DC MAIN COMB SW SUB PN PNCOM PNCOM PNCOM PNCOM PNCOM HIC HA ユニットレイアウト ...

Страница 24: ...24 AD8HR MAIN Circuit Board B B 2NAP WC06220 D010 1 ...

Страница 25: ...AD8HR 25 B B Shield MAIN Soldering ハンダ付け シールドMAIN Pattern side 2NAP WC06220 D010 1 パターン側 ...

Страница 26: ...26 AD8HR C C 1 2 3 4 5 6 D D PN Circuit Board E E to MAIN CN982 F F DC Circuit Board 2NAP WC06230 D010 1 ...