22

Virtex-6 FPGA System Monitor

UG370 (v1.1) June 14, 2010

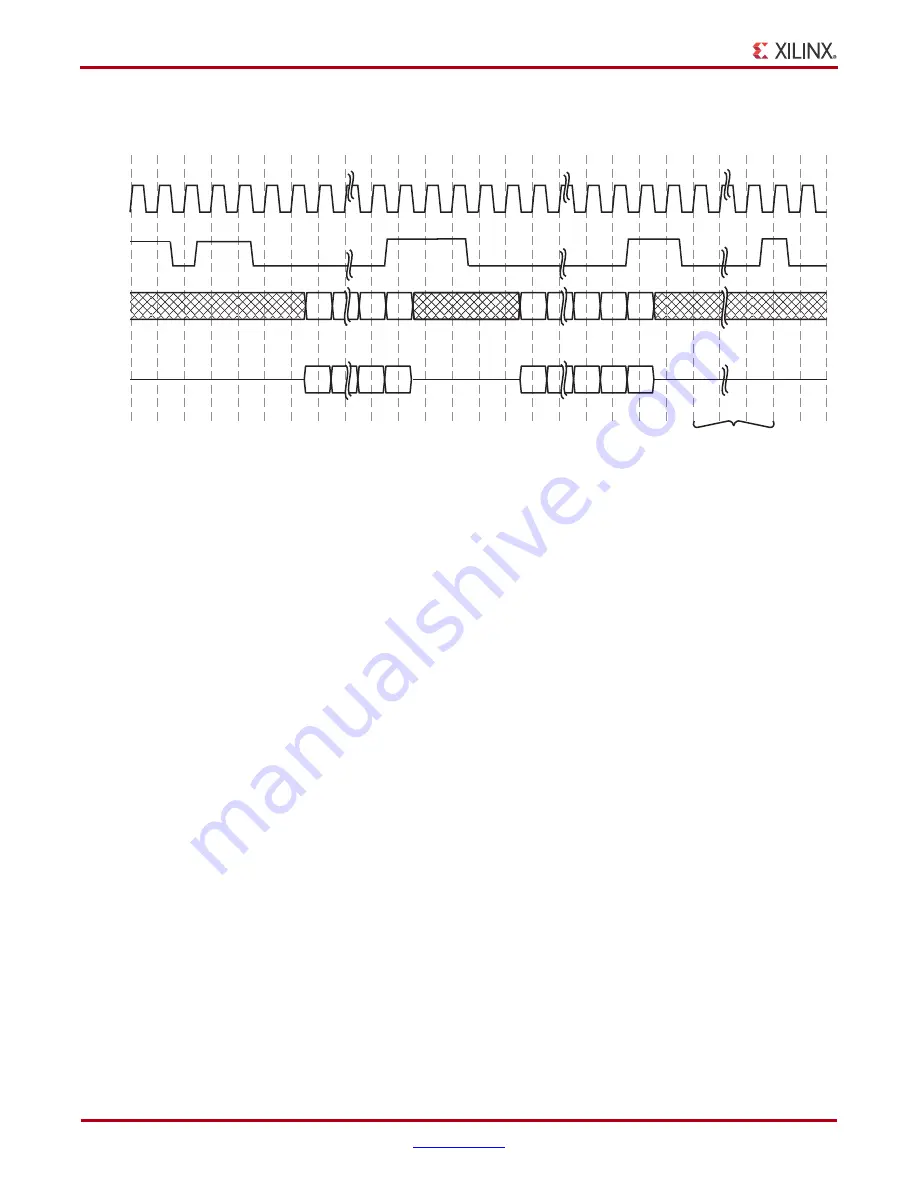

Register File Interface

System Monitor JTAG DRP Read Operation

shows the timing for a SYSMON DR Read operation. The IR should contain the

DR-scan operation SYSMON instruction. A JTAG Read from the System Monitor DRP is a

two-step operation.

•

First, the SYSMON DR is loaded with the Read DRP instruction. This instruction is

transferred to the arbitrator during the Update-DR state and then the arbitrator reads

the selected DRP register and stores the newly read 16-bit data. This operation takes

several DCLK cycles to complete.

•

During the DR-Capture phase of the next DR-scan, newly read data is transferred

from the arbitrator to the SYSMON DR. This 16-bit data (stored in the 16 LSBs of the

32-bit word) is then shifted out on TDO during the subsequent shift operation (see

). The timing diagram shows a number of idle states at the end of the first

DR-scan operation, allowing the arbitrator enough time to fetch the System Monitor

DRP data.

As mentioned previously, if the DCLK frequency is significantly faster than the TCK, these

idle states might not be required.

Note:

Implementing a DR-scan operation before the arbitrator has completed the DRP-read

operation results in old DRP data being transferred to the SYSMON DR during the DR-capture

phase.

To ensure reliable operation over all operating clock frequencies, a minimum of ten Run-

Test-Idle (RTI) states should be inserted. Multiple Read operations can be pipelined, as

shown in

. Thus, as the result of a read operation is being shifted out of the

SYSMON DR, an instruction for the next read can be shifted in.

X-Ref Target - Figure 10

Figure 10:

System Monitor JTAG DRP Write Operation

TAP Controller States

TCK

TMS

TDI

TDO

0

9

0

31

30

MSB

MSB

MSB

MSB

LSB

LSB

LSB

LSB

Load IR with

SYSMON insructions

Idle between successive

Writes to allow DRP Write

operation to finish

Old DRP Write or New

Read Data shifted out

Write DRP Command shifted into

SYSMON DR

TLR TLR RTI

RTI

RTI

RTI

DRS

DRS

DRS

IRS CIR

CDR

CDR

SIR SIR SIR SIR

SDR SDR SDR

SDR SDR

EIR

EDR UDR

UIR

UG370_10_060809

www.BDTIC.com/XILINX