5 Operation

75 SD780 Series Servo Technical Manual

reversed

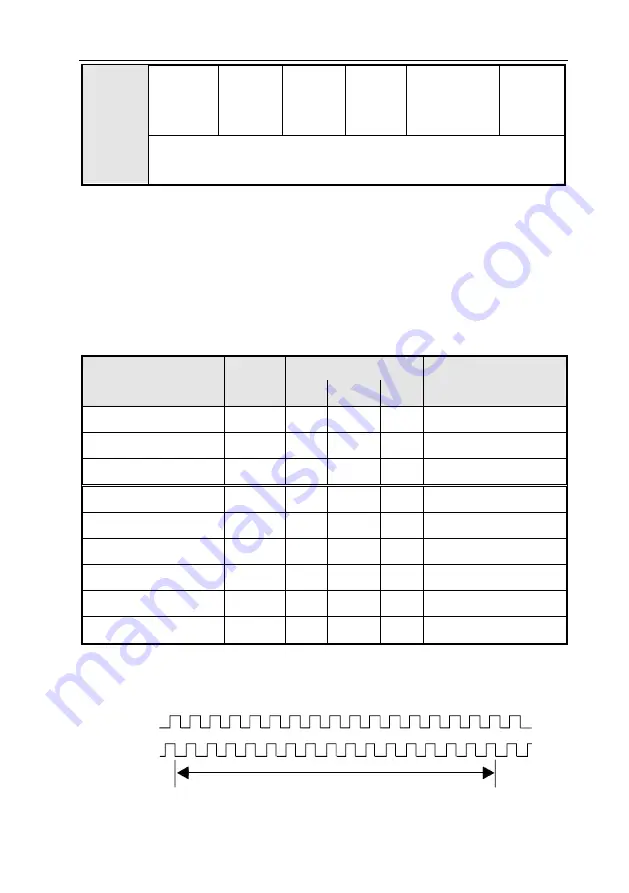

A/B pulse phase sequence logic when setting forward/reverse:

0-

Don’t revert the pulse output: When forward, A leads B.

1-

1- Revert the pulse output: When forward, B leads A .

1.

Frequency division pulse

The number of pulses per revolution from the encoder is processed inside the servo pack and then

divided down and output to the set value of Pn070.

The encoder's number of divided pulse outputs is set according to the system specifications of the

machine and the host device.

The setting of frequency division pulse number of encoder will be limited by the resolution of

encoder. The maximum output frequency of frequency division pulse of encoder shall not exceed

4MHz (after 4 times frequency), as shown in the table below:

Pulse Number of Encoder

Frequency Devision

(pulse/r)

Setting

increment

Encoder Resolution

Upper Limit of motor

Speed ( r/min)

17 bits 20 bits 23 bits

16

~

16384

1

o

o

o

6000

16386

~

32768

2

o

o

o

3000

32772

~

65536

4

o

o

o

1500

65544

~

131072

8

o

o

o

750

131088

~

262144

16

-

o

o

375

262176

~

524288

32

-

o

o

187

524352

~

1048576

64

-

o

o

93

1048704

~

2097152

128

-

-

o

46

2097408

~

4194304

256

-

-

o

23

Output example: When Pn070=16 (16 pulses per revolution), an example of the output of the

encoder-divided pulse output A-phase (PAO) signal and the encoder-divided pulse output B-phase

(PBO) signal is shown below.

1

Resolution Pn070=16

PAO

PBO

1 Resolution Pn070=16