Hardware Configuration

8

SLAU580B – June 2014 – Revised September 2016

Copyright © 2014–2016, Texas Instruments Incorporated

TSW14J10 FMC-USB Interposer Card

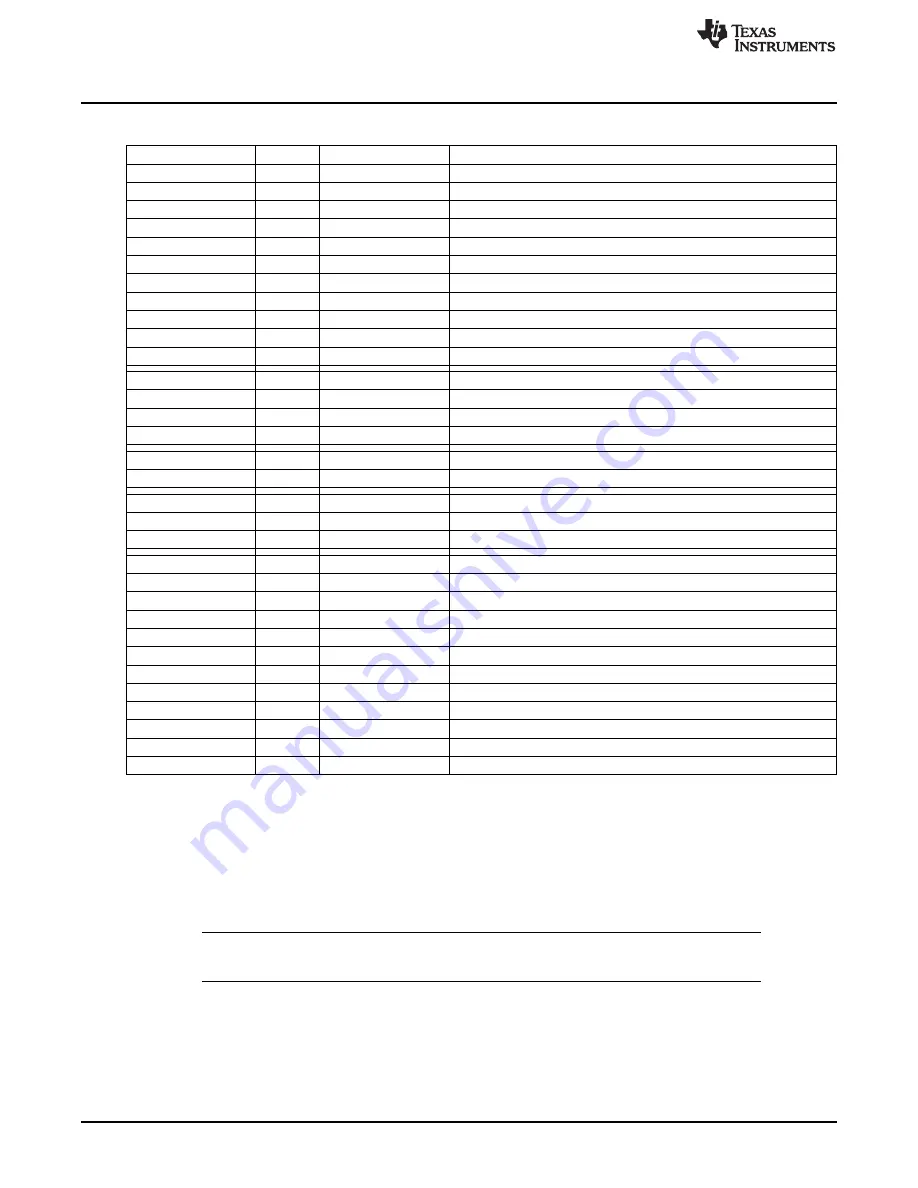

Table 3. ADC/DAC EVM FMC Connector (J4) Description of the TSW14J10 (continued)

FMC Signal Name

FMC Pin

Direction

Description

F1

F1

ADC/DAC-to-FPGA

Power good from mezzanine to carrier

D1

D1

FPGA-to-ADC/DAC

Power good from carrier to mezzanine

PRESENT

H2

ADC/DAC-to-FPGA

EVM Present indicator

ADBUS5_T

C15

USB-to-ADC/DAC

USB SPI Interface signal

ADBUS6_T

D14

USB-to-ADC/DAC

USB SPI Interface signal

ADBUS7_T

D15

USB-to-ADC/DAC

USB SPI Interface signal

BDBUS4_T

G15

USB-to-ADC/DAC

USB SPI Interface signal

BDBUS5_T

G16

USB-to-ADC/DAC

USB SPI Interface signal

BDBUS6_T

H16

USB-to-ADC/DAC

USB SPI Interface signal

BDBUS7_T

H17

USB-to-ADC/DAC

USB SPI Interface signal

CDBUS4_T

C14

USB-to-ADC/DAC

USB SPI Interface signal

OVRA

K19

ADC-to-FPGA

ADC over range indicator

OVRB

E18

ADC-to-FPGA

ADC over range indicator

OVRC

J22

ADC-to-FPGA

ADC over range indicator

OVRD

J21

ADC-to-FPGA

ADC over range indicator

FPGA_CLK2P/N

J2/J3

FPGA-to-DAC

Spare clock

FPGA_CLK1P/N

K4/K5

FPGA-to-DAC

Spare clock

LED_SYNC1

C18

FPGA-to-ADC

SYNC LED indicator

SPLED0

D17

FPGA-to-ADC

Spare LED

SPLED1

D18

FPGA-to-ADC

Spare LED

C19

C19

Spare connection

C26

C26

Spare connection

C27

C27

Spare connection

D26

D26

Spare connection

E19

E19

Spare connection

G27

G27

Spare connection

G36

G36

Spare connection

G37

G37

Spare connection

H37

H37

Spare connection

H38

H38

Spare connection

K20

K20

Spare connection

K23

K23

Spare connection

3.3.3

JTAG Connector

The TSW14J10EVM includes an industry-standard JTAG connector that is connected to the DDBUS of

the USB interface device. This interface allows the HSDC Pro GUI the capability to configure an FPGA on

a development platform if it has a corresponding JTAG connector that is routed directly to the FPGA JTAG

pins. Connect the provide JTAG cable between the TSW14J10 JTAG connector and the FPGA

development board JTAG connector.

NOTE:

FPGA development boards may require jumpers and or switches be placed in a certain

configuration to connect the JTAG connector to the FPGA JTAG pins.

If the FPGA development platform has the JTAG signals routed on the FMC connector, jumpers JP2-5

can be set (shunt pins 2-3) to route these signals to the FMC connector instead of the JTAG connector.