MSP430FG47x

MIXED SIGNAL MICROCONTROLLER

SLAS580D -- OCTOBER 2008 -- REVISED MARCH 2011

59

POST OFFICE BOX 655303

DALLAS, TEXAS 75265

electrical characteristics over recommended ranges of supply voltage and operating free-air

temperature (unless otherwise noted) (continued)

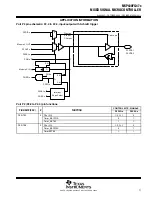

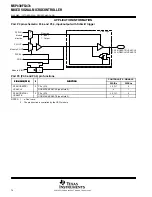

USCI (I2C mode) (see Figure 35)

PARAMETER

TEST CONDITIONS

V

CC

MIN

TYP

MAX UNIT

f

USCI

USCI input clock frequency

Internal: SMCLK, ACLK

External: UCLK

Duty cycle = 50%

10%

f

SYSTEM

MHz

f

SCL

SCL clock frequency

2.2 V/3 V

0

400

kHz

t

Hold time (repeated) START

f

SCL

100kHz

2.2 V/3 V

4.0

s

t

HD,STA

Hold time (repeated) START

f

SCL

> 100kHz

2.2 V/3 V

0.6

s

t

Set p time for a repeated START

f

SCL

100kHz

2.2 V/3 V

4.7

s

t

SU,STA

Setup time for a repeated START

f

SCL

> 100kHz

2.2 V/3 V

0.6

s

t

HD,DAT

Data hold time

2.2 V/3 V

0

ns

t

SU,DAT

Data setup time

2.2 V/3 V

250

ns

t

SU,STO

Setup time for STOP

2.2 V/3 V

4.0

s

t

Pulse width of spikes suppressed by

2.2 V

50

150

600

ns

t

SP

Pulse width of spikes suppressed by

input filter

3 V

50

100

600

ns

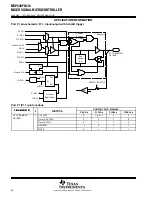

SDA

SCL

1/fSCL

tHD,DAT

tSU,DAT

tHD,STA

tSU,STA tHD,STA

tSU,STO

tSP

Figure 35. I2C Mode Timing

Содержание MSP430FG47x

Страница 91: ......