MSP430FG47x

MIXED SIGNAL MICROCONTROLLER

SLAS580D -- OCTOBER 2008 -- REVISED MARCH 2011

73

POST OFFICE BOX 655303

DALLAS, TEXAS 75265

APPLICATION INFORMATION

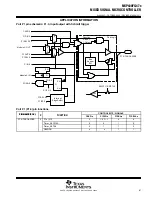

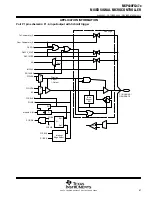

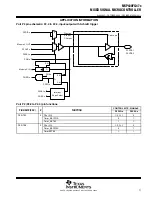

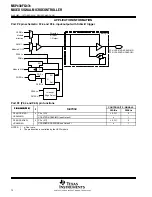

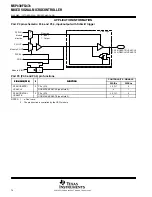

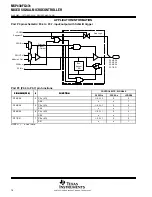

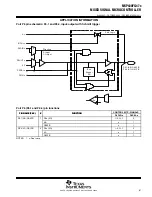

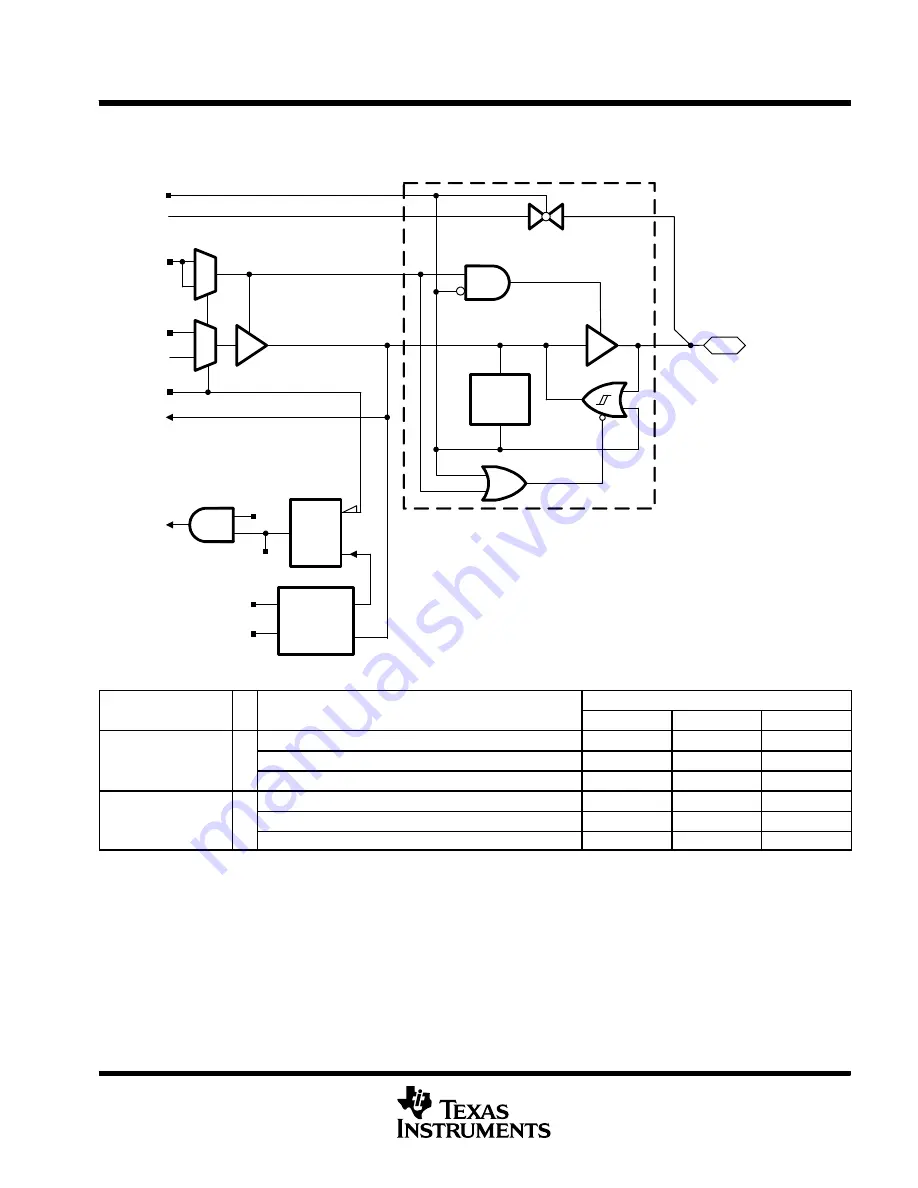

Port P2 pin schematic: P2.6 and P2.7, inpututput with Schmitt trigger

P2.6/CAOUT/S2

P2.7/S3

Direction

0: Input

1: Output

P2SEL.x

P2DIR.x

P2IN.x

0/1

P2OUT.x

Pad Logic

1

0

1

0

Bus

Keeper

EN

Segment Sy

LCDS0

P2IRQ.x

Interrupt

Edge Select

Q

EN

Set

P2SEL.x

P2IES.x

P2IFG.x

P2IE.x

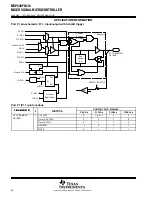

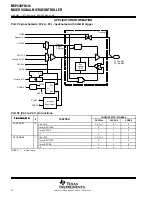

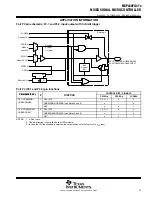

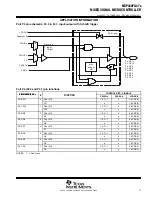

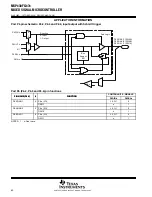

Port P2 (P2.6 and P2.7) pin functions

PIN NAME (P2 X)

X

FUNCTION

CONTROL BITS / SIGNALS

PIN NAME (P2.X)

X

FUNCTION

P2DIR.x

P2SEL.x

LCDS0

P2.6/CAOUT/S2

6

P2.x (I/O)

I: 0, O: 1

0

0

/

/

CAOUT

1

1

0

S2

x

x

1

P2.7/S3

7

P2.x (I/O)

I: 0, O: 1

0

0

/

V

ss

1

1

0

S3

x

x

1

NOTES: 1. x: Don’t care.

Содержание MSP430FG47x

Страница 91: ......