Sun Microelectronics

340

UltraSPARC User’s Manual

1.

ECAD<19:0> for UltraSPARC-II: corresponds to Physical Address <23:4>

2.

ECAT<17:0> for UltraSPARC-II: corresponds to Physical Address <23:6>

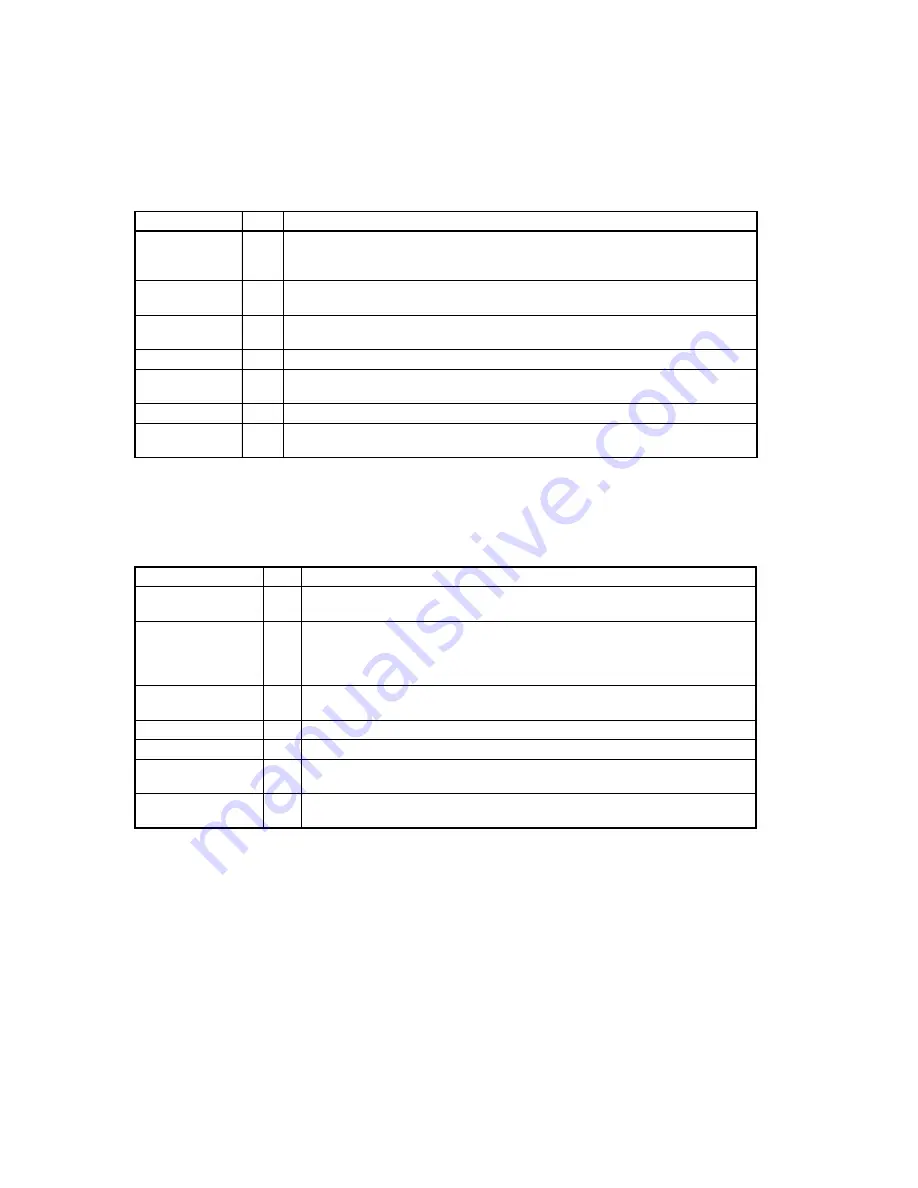

E.2.5 Clock Interface Pins

1.

SCLK_MODE is present only on UltraSPARC-I.

2.

LOOP_CAP is present only on UltraSPARC-I.

3.

PHASE_DET_CLK is present only on UltraSPARC-II.

4.

ECACHE_22_MODE is present only on UltraSPARC-II.

5.

MCAP is present only on UltraSPARC-II.

BYTEWE_L<15:0>

O

Byte write enables for the E-Cache SRAMs. Bit 0 controls EDATA<127:120>. Bit 15 con-

trols EDATA<7:0>. Byte write control is necessary because the first-level data cache is

write-through. Synchronous to processor clock.

ECAD<17:0>

1

O

Address for E-Cache data SRAMS. Corresponds to physical address <21:4>. Allows a

maximum 4mbyte E-Cache. Synchronous to processor clock.

ECAT<15:0>

2

O

Address for E-Cache tag SRAMS. Corresponds to physical address <21:6>. Allows a

maximum 4Mb E-Cache. Synchronous to processor clock.

DSYN_WR_L

O

Write enable for E-Cache data SRAMS. Active low. Synchronous to processor clock.

DOE_L

O

Active low operation enable for all E-Cache data SRAM reads and writes. Synchronous

to processor clock.

TSYN_WR_L

O

Write enable for E-Cache tag SRAMS. Active low. Synchronous to processor clock.

TOE_L

O

Active low operation enable for all E-Cache tag SRAM reads and writes. Active low.

Synchronous to processor clock.

Table E-5

Clock Interface Pins

Symbol

Type

Name and Function

CLKA, CLKB

I

These pins provide UltraSPARC with its primary differential PECL clock source. Full

details of clock requirements are presented in another chapter.

SYSCLKA, SYSCLKB

I

Buffered differential versions of the PECL system clock, which is a synchronous one

half or one third submultiple of the primary clock. They are used to generate the

phase signal, which allows UltraSPARC to synchronize communication to the sys-

tem and UDBs.

SCLK_MODE

1

I

Asserted if the system clock frequency is one third of the processor clock frequency,

deasserted if the system clock frequency is one half of the processor clock frequency.

LOOP_CAP

2

I

Provision for external PLL loop filter capacitor. Currently not needed.

PHASE_DET_CLK

3

I

Used only for testing PLL Bypass mode.

ECACHE_22_MODE

4

I

Asserted if 2–2 (Register-latch) SRAMS are used in the E-Cache. Deasserted for 1–1–

1 (pipelined) E-Cache SRAMS. Hardwired externally.

MCAP<3:0>

5

I

Implementation-dependent module capability bits. May be used to indicate speed

range of the module. Hardwired externally.

Table E-4

External Cache Interface Pins (Continued)

Symbol

Type

Name and Function

Artisan Technology Group - Quality Instrumentation ... Guaranteed | (888) 88-SOURCE | www.artisantg.com