Sun Microelectronics

339

E. Pin and Signal Descriptions

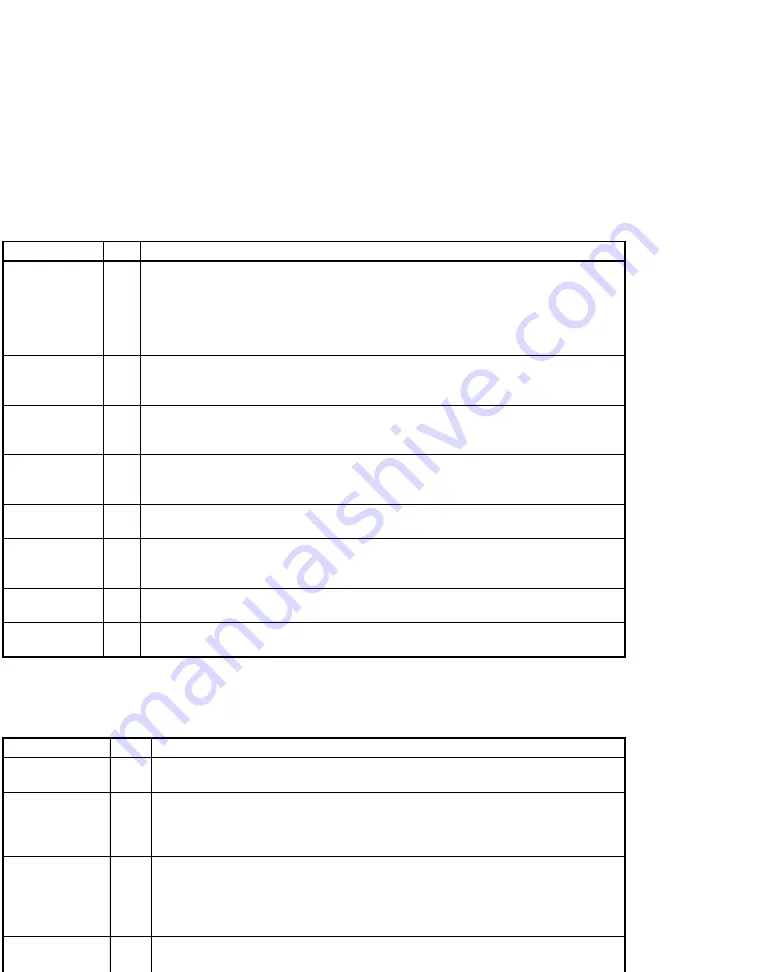

E.2.3 System Interface Pins

E.2.4 E-Cache Interface Pins

Table E-3

System Interface Pins

Symbol

Type

Name and Function

SYSADDR<35:0>

I/O 36-bit bidirectional packet-switched request bus, which includes 1-bit odd-parity. It carries

address bits PA<40:4> of a 41-bit physical address space in the P_REQ and S_REQ transac-

tions described in Chapter 7, “UltraSPARC External Interfaces.” A valid packet on the

SYSADDR bus is identified by the driver asserting the

Addr_valid

signal. The

SYSADDR and SYSDATA buses are independent, and an address is associated with its

data through ordering rules discussed in a later section. Synchronous to system clock.

ADDR_VALID

I/O Bidirectional radial signal between UltraSPARC and the system. Driven by UltraSPARC to

initiate SYSADDR transactions to the system. Driven by the system to initiate coherency,

interrupt or slave transactions to UltraSPARC. Synchronous to system clock.

NODEX_RQ

O

SYSADDR bus arbitration request. Asserted when UltraSPARC wants to acquire the

SYSADDR bus. Connected to other master ports which share this address bus and the sys-

tem. Synchronous to system clock.

NODE_RQ<2:0>

I

SYSADDR bus arbitration request from up to three other port masters that might be shar-

ing the SYSADDR bus. Used by UltraSPARC for the distributed SYSADDR arbitration

protocol. Synchronous to system clock.

SC_RQ

I

SYSADDR bus arbitration request from the system. Used by UltraSPARC for the distrib-

uted SYSADDR bus arbitration protocol. Synchronous to system clock.

S_REPLY<3:0>

I

System Reply packet from the system to UltraSPARC. Used by UltraSPARC for flow con-

trol and initiating data transfers between the system and the data buffer chips. Synchro-

nous to system clock.

P_REPLY<4:0>

O

Processor reply packet, driven by UltraSPARC to the system to acknowledge a request

from the system. Synchronous to system clock.

DATA_STALL

I

This signal is asserted to hold UDB output data to the system, or signal the delay in arrival

of input data from the system.

Table E-4

External Cache Interface Pins

Symbol

Type

Name and Function

EDATA<127:0>

I/O

E-Cache Data bus. Connects UltraSPARC to the E-Cache data rams and the data buffer

chips. Synchronous to processor clock.

EDPAR<15:0>

I/O

Byte parity for EDATA. Odd parity is driven by UltraSPARC when driving EDATA, and

checked by UltraSPARC when E-Cache SRAMs or the data buffer chips are driving

EDATA. EDPAR<0> serves as the parity for EDATA<7:0>. Synchronous to processor

clock.

TDATA<24:0>

I/O

Bidirectional data bus for E-Cache tag RAMs. Bits 24:22 carry the MOESI state: Modi-

fied, Owned, Exclusive, Shared, Invalid. Bits 21:0 carry the physical address bits

<40:19>. This allows a minimum cache size of 512Kb. All of the TDATA bits are used,

even when the E-Cache is greater than 512Kbytes. This is because there is no sizing in

the tag compare for E-Cache hit generation. Synchronous to processor clock.

TPAR<3:0>

I/O

E-Cache tag RAM byte parity. Odd Parity is driven by UltraSPARC when driving

TDATA, and checked by UltraSPARC when E-Cache SRAMs are driving. TPAR<0> cov-

ers TDATA<7:0>. Synchronous to processor clock.

Artisan Technology Group - Quality Instrumentation ... Guaranteed | (888) 88-SOURCE | www.artisantg.com