STM32F42xx and STM32F43xx silicon limitations

STM32F42xx and STM32F43xx

DocID023833 Rev 5

2

STM32F42xx and STM32F43xx silicon limitations

gives quick references to all documented limitations.

Legend for

: A = workaround available; N = no workaround available; P = partial

workaround available, ‘-’ and grayed = fixed.

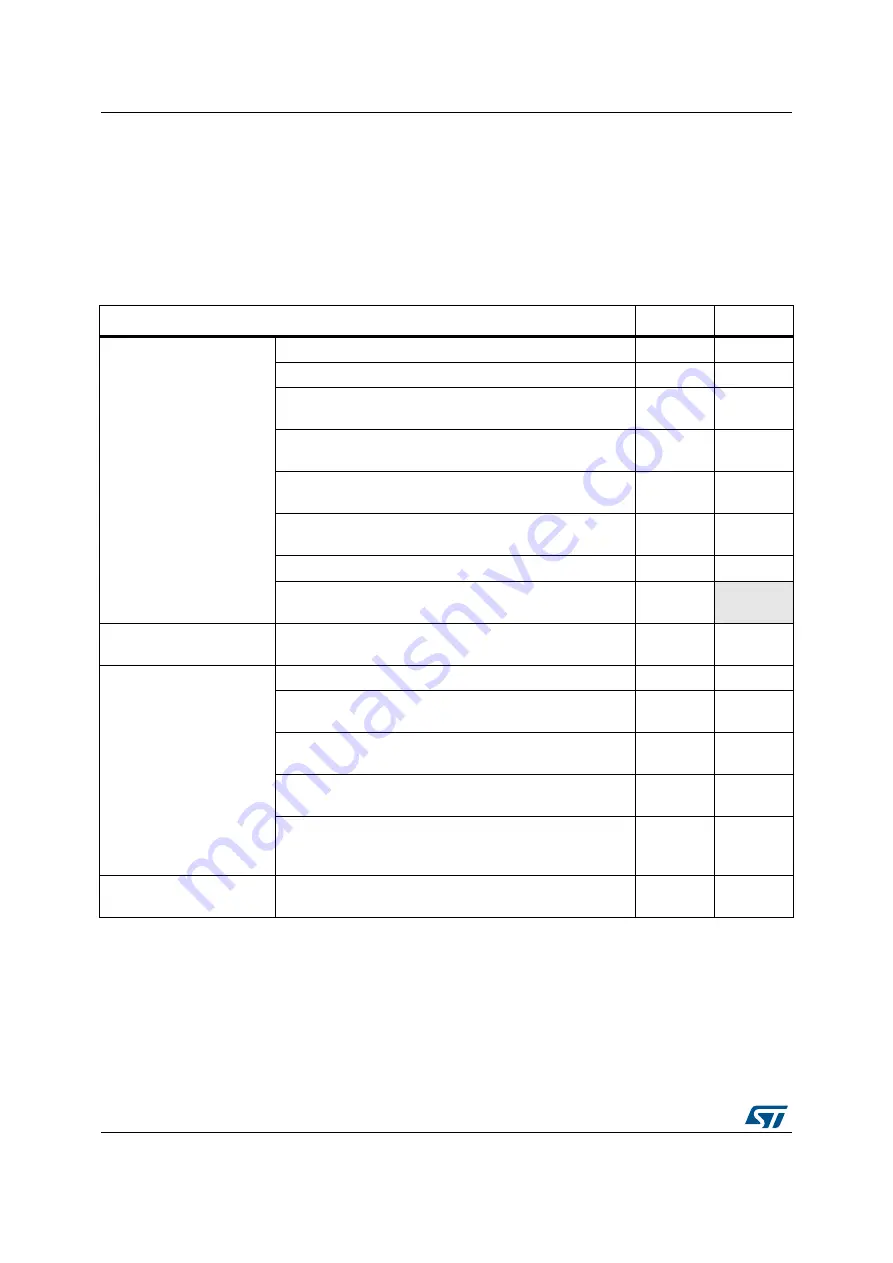

Table 4. Summary of silicon limitations

Links to silicon limitations

Revision A Revision Y

Section 2.1: System

limitations

Section 2.1.1: Debugging Stop mode and system tick timer

A

A

Section 2.1.2: Debugging Stop mode with WFE entry

A

A

Section 2.1.3: Wakeup sequence from Standby mode

when using more than one wakeup source

A

A

Section 2.1.4: Full JTAG configuration without NJTRST pin

cannot be used

A

A

Section 2.1.5: MPU attribute to RTC and IWDG registers

could be managed incorrectly

A

A

Section 2.1.6: Delay after an RCC peripheral clock

enabling

A

A

Section 2.1.7: Internal noise impacting the ADC accuracy

A

A

Section 2.1.8: Over-drive and Under-drive modes

unavailability

N

-

Section 2.2: IWDG

peripheral limitation

Section 2.2.1: RVU and PVU flags are not reset in STOP

mode

A

A

Section 2.3: I2C peripheral

limitations

Section 2.3.1: SMBus standard not fully supported

A

A

Section 2.3.2: Start cannot be generated after a misplaced

Stop

A

A

Section 2.3.3: Mismatch on the “Setup time for a repeated

Start condition” timing parameter

A

A

Section 2.3.4: Data valid time (tVD;DAT) violated without

the OVR flag being set

A

A

A

A

Section 2.4: I2S peripheral

limitation

Section 2.4.1: In I2S slave mode, WS level must be set by

the external master when enabling the I2S

A

A