Obsolete Product(s) - Obsolete Product(s)

Obsolete Product(s) - Obsolete Product(s)

Electrical characteristics

ST7LITEUS2, ST7LITEUS5

12.3 Operating

conditions

12.3.1

General operating conditions

T

A

= -40 to +125 °C unless otherwise specified.

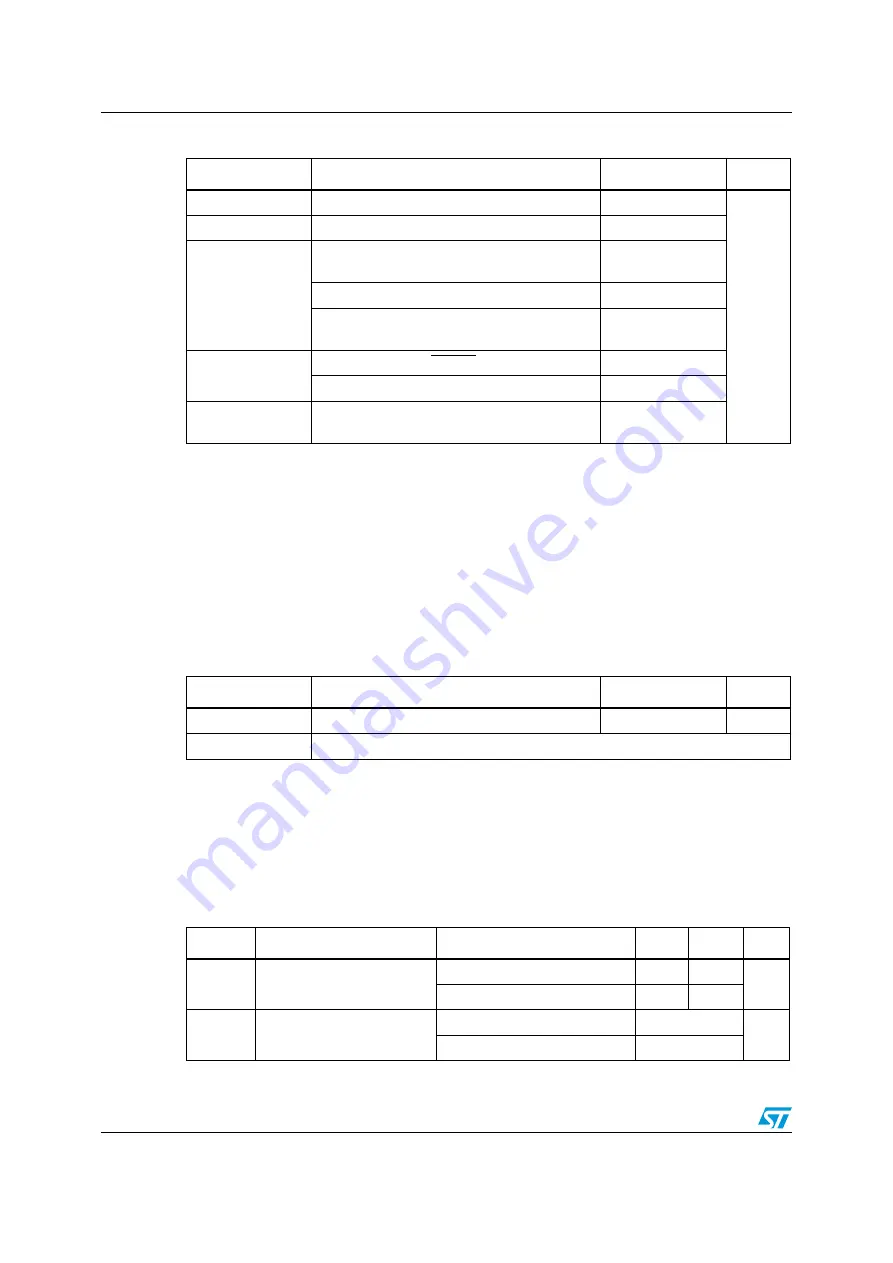

Table 44.

Current characteristics

Symbol

Ratings

Maximum value

Unit

I

VDD

Total current into V

DD

power lines (source)

(1)

1.

All power (V

DD

) and ground (V

SS

) lines must always be connected to the external supply.

75

mA

I

VSS

Total current out of V

SS

ground lines (sink)

150

I

IO

Output current sunk by any standard I/O and

control pin

20

Output current sunk by any high sink I/O pin

40

Output current source by any I/Os and control

pin

-25

I

INJ(PIN)

(2)(3)

2.

I

INJ(PIN)

must never be exceeded. This is implicitly insured if V

IN

maximum is respected. If V

IN

maximum

cannot be respected, the injection current must be limited externally to the I

INJ(PIN)

value. A positive

injection is induced by V

IN

>V

DD

while a negative injection is induced by V

IN

<V

SS

.

3.

Negative injection disturbs the analog performance of the device. In particular, it induces leakage currents

throughout the device including the analog inputs. To avoid undesirable effects on the analog functions,

care must be taken:

- Analog input pins must have a negative injection less than 0.8 mA (assuming that the impedance of the

analog voltage is lower than the specified limits)

- Pure digital pins must have a negative injection less than 1.6 mA. In addition, it is recommended to inject

the current as far as possible from the analog input pins.

Injected current on RESET pin

± 5

Injected current on any other pin

(4)

4.

When several inputs are submitted to a current injection, the maximum

Σ

I

INJ(PIN)

is the absolute sum of the

positive and negative injected currents (instantaneous values). These results are based on

characterisation with

Σ

I

INJ(PIN)

maximum current injection on four I/O port pins of the device.

± 5

Σ

I

INJ(PIN)

Total injected current (sum of all I/O and control

pins)

± 20

Table 45.

Thermal characteristics

Symbol

Ratings

value

Unit

T

STG

Storage temperature range

-65 to +150

°C

T

J

Maximum junction temperature (see

Section 13: Package characteristics

)

Table 46.

General operating conditions

Symbol

Parameter

Conditions

Min

Max

Unit

V

DD

Supply voltage

f

CPU

= 4 MHz max.

2.4

5.5

V

f

CPU

= 8 MHz max.

3.3

5.5

f

CPU

CPU clock frequency

3.3 V

≤

V

DD

≤

5.5 V

up to 8

MHz

2.4 V

≤

V

DD

<

3.3 V

up to 4

Obsolete Product(s) - Obsolete Product(s)