DocID13284 Rev 2

427/564

UM0404

CAN modules

Status interrupts

A Status Interrupt is generated by bits

BOff

and

EWarn

(Error Interrupt) or by

RxOk

,

TxOk

,

and

LEC

(Status Change Interrupt) assumed that the corresponding enable bits in the CAN

Control Register are set. A change of bit

EPass

or a write to

RxOk

,

TxOk

, or

LEC

will never

generate a Status Interrupt.

Reading the Status Register will clear the Status Interrupt value (8000h) in the Interrupt

Register, if it is pending.

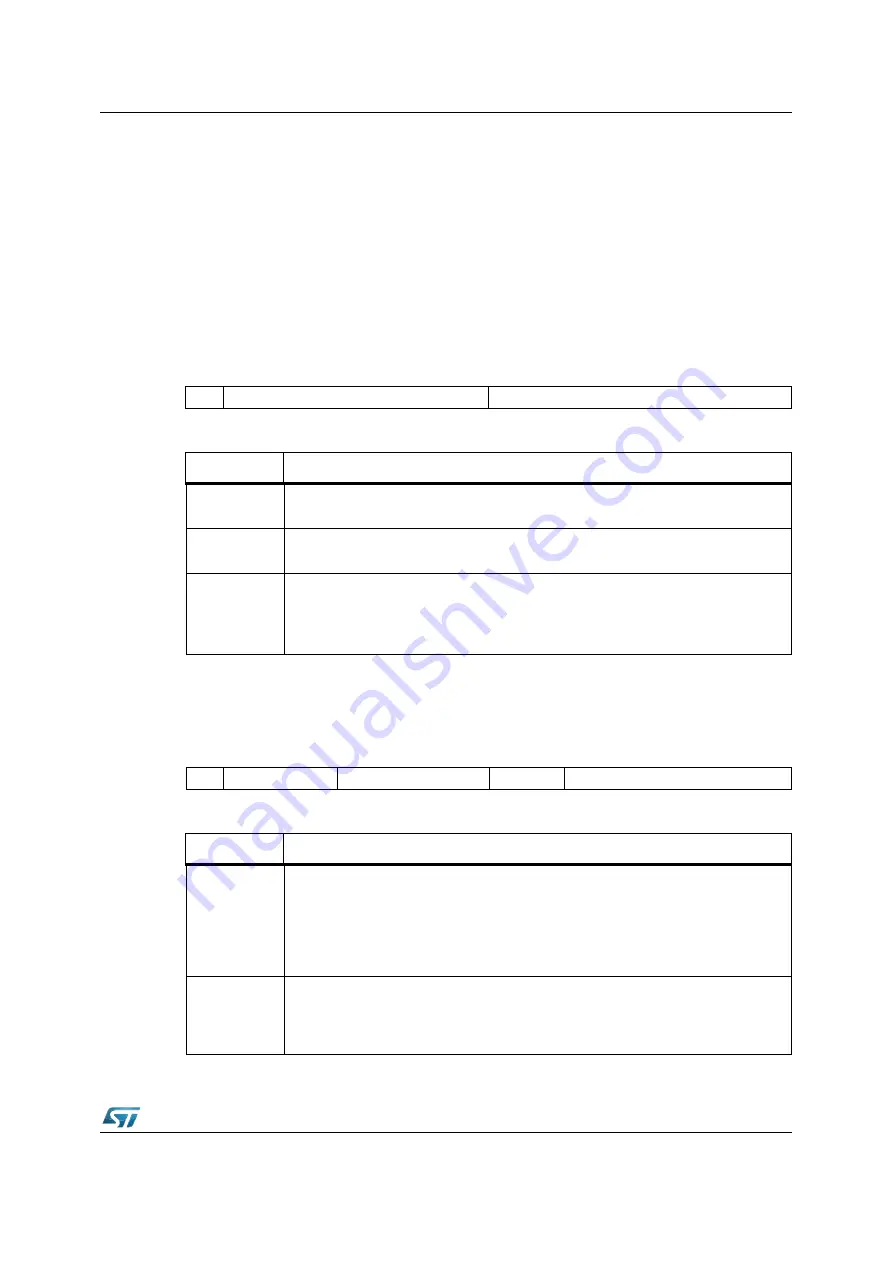

Error counter

CAN1EC (EF04h)

XBUS

Reset Value: 0000h

CAN2EC (EE04h)

XBUS

Reset Value: 0000h

Bit timing register

CAN1BTR (EF06h)

XBUS

Reset Value: 2301h

CAN2BTR (EE06h)

XBUS

Reset Value: 2301h

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

0

RP

REC(6:0)

TEC(7:0)

R

R

R

Bit

Function

TEC(7:0)

Transmit Error Counter

Actual state of the Transmit Error Counter. Values between 0 and 255.

REC(6:0)

Receive Error Counter

Actual state of the Receive Error Counter. Values between 0 and 127.

RP

Receive Error Passive

’0’: The Receive Error Counter is below the

error passive

level.

’1’: The Receive Error Counter has reached the

error passive

level as defined in the

CAN Specification.

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

0

-

TSeg2

TSeg1

SJW

BRP

RW

RW

RW

RW

Bit

Function

BRP

Baud Rate Prescaler

Value by which the CPU clock frequency is divided for generating the bit time

quanta. The bit time is built up from a multiple of this quanta. Valid values for the

Baud Rate Prescaler are 01h-3Fh (0…63). The actual interpretation by the

hardware of this value is such that one more than the value programmed here is

used.

SJW

(Re)Synchronization Jump Width

Valid programmed values are 0h-3h (0...3). The actual interpretation by the

hardware of this value is such that one more than the value programmed here is

used.