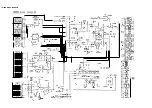

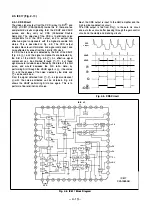

2-6. IC91 5 (CXD1 159Q)

Pin @ of IC91 5 (CXD1 1 59Q) receives the 1 4 MHz clock

from Pin @ of IC91 6 (CXD1 256R) and generates various

sync signals. The block diagram, timing chart and pin

functions are shown in Fig. 2-1 3, 2-1 4 and 2-1 5 and Table

2-4 respectively.

FSC1

1 /4

FSCO

1 /5

1 /227

1 /4

CLK1

1/65

CLKO

H-DECODER

IC915

CXD1 1 59Q

iii

>

0

Cl

:::c

0

Cl

>

()

z

�

g

u.

Fig. 2-13. IC91 5 Block Diagram

- 4-1 8 -

PHASE

COMPARATOR

UJ

Cl

z

�

Cl

z

�

COM P

P SEL

MODE

TEST

EXT

HR

VR

LR

V I NT