Rev.2.00 Oct 16, 2006 page 307 of 354

REJ09B0340-0200

M30245 Group

3. DMAC Applications

3.5 Memory to Memory DMA Transfer

The following are steps for changing both source address and destination address to transfer

data from memory to another. The DMA transfer utilizes the workings that assign a higher priority

to the DMA0 transfer if transfer requests simultaneously occur in two DMA channels. Figure

3.5.1 shows the operation timing, Figure 3.5.2 shows the block diagram, and Figures 3.5.3 and

3.5.4 show the set-up procedure.

Use the following peripheral functions:

• Timer mode of timer A

• Two DMAC channels

• One-byte temporary RAM (address 0800

16

)

(1) Transfer the content of memory extending over 128 bytes from address F6000

16

to a 128-

byte area starting from address 00400

16

. Transfer the content every time a timer A0 interrupt

request occurs.

(2) Use DMA0 for a transfer from the source to built-in memory, and DMA1 for a transfer from

built-in memory to the destination.

(1) A timer A interrupt request occurs. Though both a DMA0 transfer request and a DMA1 trans-

fer request occur simultaneously, the former is executed first.

(2) DMA0 receives a transfer request and transfers data from the source to the built-in memory.

At this time, the source address is incremented.

(3) Next, DMA1 receives a transfer request and transfers data involved from built-in memory to

the destination. At this time, the destination address is incremented.

Overview

Specifications

Operation

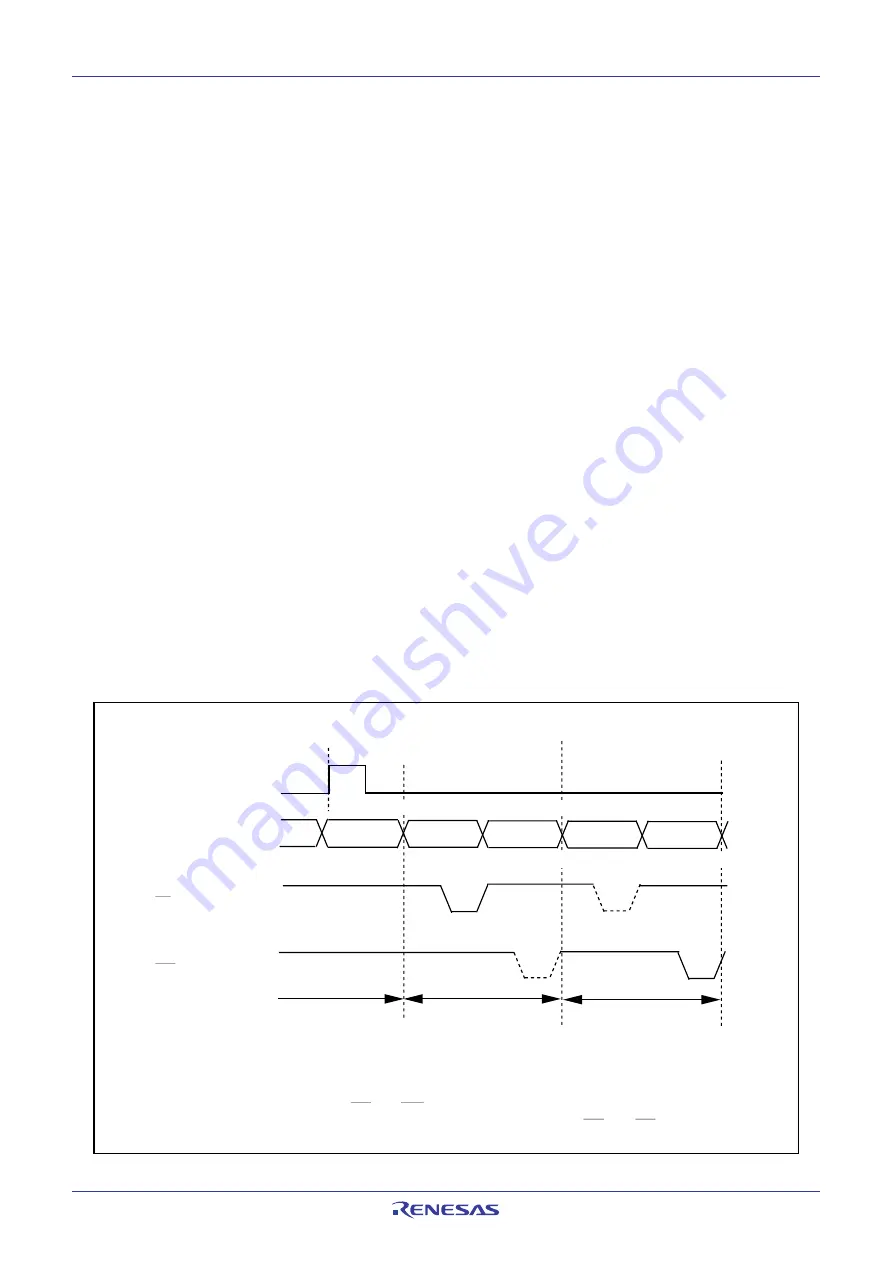

Figure 3.5.1. Operation timing of memory to memory DMA transfer

Timer A0

transfer request

Address bus

“0”

“1”

“0”

“1”

“0”

“1”

(1) Transfer request generation

(2) Start DMA0 transferring

(3) Start DMA1 transferring

Instruction cycle

DMA0 operation

DMA1 operation

F6000

16

0800

16

0800

16

00400

16

WR signal

RD signal

Source address

Destination address

Source address

Destination address

The DMA0 operation and DMA1 operation are not necessarily executed in succession

due to the a cycle steal operation.

The instruction cycle varies from instruction to instruction.

Since the parts of the RD and WR signals shown in short-dash lines vary in step with

writing to the internal RAM, waveforms are not output to the RD and WR pins.

Note 1:

Note 2:

Note 3:

Содержание M16C FAMILY

Страница 12: ...Chapter 1 Hardware...

Страница 13: ...See M30245 group datasheet...

Страница 14: ...Chapter 2 Peripheral Functions Usage...

Страница 303: ...THIS PAGE IS BLANK FOR REASONS OF LAYOUT...

Страница 304: ...Chapter 3 Examples of Peripheral Functions Applications...

Страница 340: ...Chapter 4 External Buses...

Страница 361: ...THIS PAGE IS BLANK FOR REASONS OF LAYOUT...

Страница 362: ...Chapter 5 Standard Characteristics...

Страница 369: ...1753 Shimonumabe Nakahara ku Kawasaki shi Kanagawa 211 8668 Japan M30245 Group REJ09B0340 0200 User s Manual...