Rev.2.00 Oct 16, 2006 page 290 of 354

REJ09B0340-0200

M30245 Group

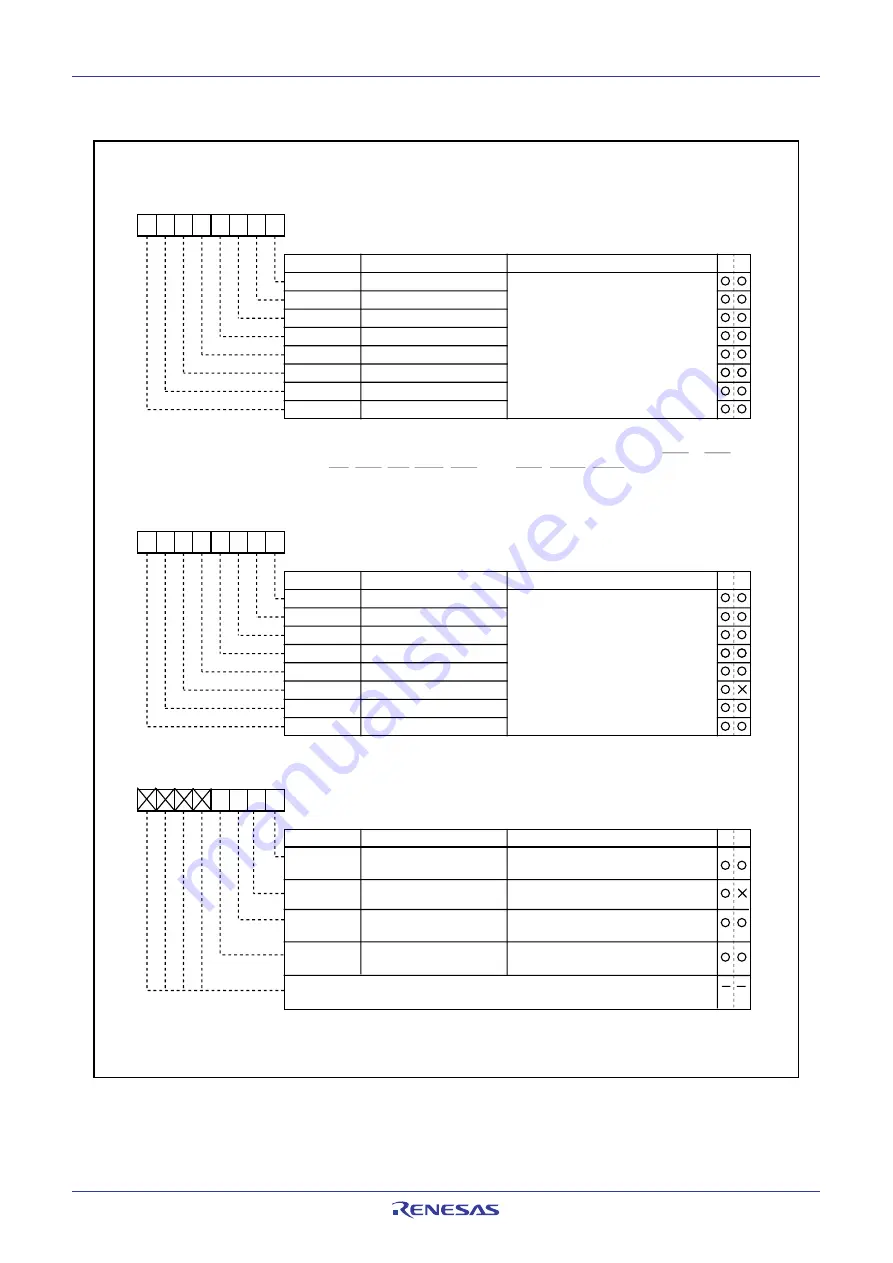

2. Programmable I/O Ports

Figure 2.17.4. Programmable I/O ports-related registers (3)

Port Pi register (Note 2)

Symbol

Address

When reset

Pi (i = 0 to 7, 10)

03E0

16

, 03E1

16

, 03E4

16

, 03E5

16

, 03E8

16

Indeterminate

03E9

16

, 03EC

16

, 03ED

16

, 03F4

16

Indeterminate

Bit name

Function

Bit symbol

W

R

b7

b6

b5

b4

b3

b2

b1

b0

Pi_0

Port Pi

0

register

Pi_1

Port Pi

1

register

Pi_2

Port Pi

2

register

Pi_3

Port Pi

3

register

Pi_4

Port Pi

4

register

Pi_5

Port Pi

5

register

Pi_6

Port Pi

6

register

Pi_7

Port Pi

7

register

Data is input and output to and from

each pin by reading and writing to

and from each corresponding bit

0 : “L” level data

1 : “H” level data (Note 1)

(i = 0 to 7, 10)

Port P8 register

Symbol

Address

When reset

P8

03F0

16

Indeterminate

Bit name

Function

Bit symbol

W

R

b7

b6

b5

b4

b3

b2

b1

b0

P8_0

Port P8

0

register

P8_1

Port P8

1

register

P8_2

Port P8

2

register

P8_3

Port P8

3

register

P8_4

Port P8

4

register

P8_5

Port P8

5

register

P8_6

Port P8

6

register

P8_7

Port P8

7

register

Data is input and output to and from

each pin by reading and writing to

and from each corresponding bit

(except for P8

5

)

0 : “L” level data

1 : “H” level data

A

AA

A

AA

A

AA

A

A

AA

AA

A

AA

A

AA

A

AA

A

AA

A

AA

A

AA

A

AA

A

A

AA

AA

A

AA

A

AA

A

A

AA

AA

A

AA

A

A

AA

AA

A

Note 1:

Since P7

0

and P7

1

are N-channel open drain ports, the data is high-impedance.

Note 2: In memory expansion and microprocessor mode, the contents of

corresponding port Pi register of pins A

0

to A

19

, D

0

to D

15

, CS

0

to CS

3

,

RD, WRL/WR, WRH/BHE, ALE, RDY, HOLD, HLDA and BCLK cannot

be modified.

Port P9 register

Symbol

Address

When reset

P9

03F1

16

Indeterminate

Bit name

Function

Bit symbol

W

R

b7

b6

b5

b4

b3

b2

b1

b0

P9_0

Port P9

0

register

VbusDTCT

Vbus detect state bit

P9_2

Port P9

2

register

P9_3

Port P9

3

register

0 : “L” level data

1 : “H” level data

A

AA

A

AA

A

AA

A

Nothing is assigned.

Write “0” when writing to these bits. The value is indeterminate if read.

0 : “L” level data

1 : “H” level data

0 : “L” level data

1 : “H” level data

0 : Not powered

1 : Powered (Note 1)

Note 1: This pin cannot be used for GPI/O. This bit reads “0” when Vbus detect is disabled.

Содержание M16C FAMILY

Страница 12: ...Chapter 1 Hardware...

Страница 13: ...See M30245 group datasheet...

Страница 14: ...Chapter 2 Peripheral Functions Usage...

Страница 303: ...THIS PAGE IS BLANK FOR REASONS OF LAYOUT...

Страница 304: ...Chapter 3 Examples of Peripheral Functions Applications...

Страница 340: ...Chapter 4 External Buses...

Страница 361: ...THIS PAGE IS BLANK FOR REASONS OF LAYOUT...

Страница 362: ...Chapter 5 Standard Characteristics...

Страница 369: ...1753 Shimonumabe Nakahara ku Kawasaki shi Kanagawa 211 8668 Japan M30245 Group REJ09B0340 0200 User s Manual...