VSX-74TXVi

257

5

6

7

8

5

6

7

8

C

D

F

A

B

E

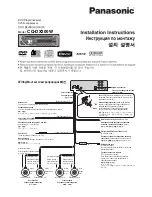

F2602E-01 (DIGITAL MOTHER ASSY : IC281)

• XM/DT IC

Pin Arrangement (Top view)

LSDP_TXRX 1

HSDP_EN

36

VSS 2

VSS

35

SC_TX_OUT 3

HSDP_CLK

34

VDD 4

VDD

33

SC_RX_IN 5

HSDP_DATA

32

VSS 6

VSS

31

COMMAND_SEL 7

TEST

30

VDD 8

VSS

29

IRQ# 9

OSC_IN

28

VSS 10

VDD

27

RESET# 11

OSC_OUT

26

SLAVE_SEL

TX+ / TX-

I2S_OCLK (Mstr only)

RX+ / RX-

TX_DIGL_OUT

RX_DIG_IN

TX_EN~

12

COMM_RX_DIG

13

COMM_TX_DIG

14

COMM_TX_EN

15

VSS

16

VDD

17

COMM_RX_P

18

COMM_RX_M

19

VDD

20

VSS

21

COMM_TX_M

22

COMM_TX_P

23

VSS

24

VSS

25

OSC_IN

OSC_OUT

SLAVE_SEL

TEST

Block Diagram

SAII_EN

48

SAII_DATA

47

VDD

46

SAII_CLK

45

VSS

44

I2S_OCLK

43

VSS

42

I2S_LRCLK

41

VDD

40

I2S_SCLK

39

VSS

38

I2S_DATA

37

OSC

RAM

XMDTIC

High Spd

Data Port

(HSDP)

Inter-IC

Sound

(I2S)

COMM

ENGINE

COMM

I/F

2

2

SC_RX_IN

SC_TX_OUT

RESET~

ERR_IRQ~

COMMAND_SEL

Sys Ctrlr

(CBM)

Bus I/F

I2S_LRCLK (M=o; S=i)

I2S_SCLK (M=o; S=i)

I2S_DATA (M=o; S=i)

HSDP_EN (M=o; S=i)

HSDP_CLK (M=o; S=i)

HSDP_DATA (M=o; S=i)

SAII

SAII_EN (M=i; S=o)

SAII_CLK (M=o; S=i)

SAII_DATA (M=o; S=i)

Low Spd

Data Port

(LSDP)

LSDP_TXRX (M=o; S=i)