GRL-PCIE5-CEM-RXA User Guide and MOI

Rev7.0

© Granite River Labs 2022 Version 7.0, June 2022. Updated 06.29.2022

Page 61 of 123

2.

In the drop-

down Menu, select ‘Initialize’ to start using the application.

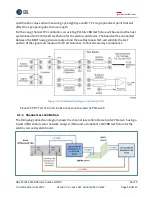

8.1.6

Amplitude Calibration Adjustment

Adjust the Amplitude with Scope markers to 800 mVpp(diff) using the following configuration.

a)

BERT Settings:

•

General Output: ON

•

Select SI-PPG and Emphasis tab- Emphasis Function: OFF, Manual Setting pane-

Standard/Preset: PCIe5, De-Emphasis, Preset 4

•

Select the Pattern tab- Test Pattern: Using Preset 4, with 64 ones followed by 64 zeros

followed by 128 bits of a 1010 clock pattern at 32.0 GT/s

•

Select the Misc1 tab- Aux Output: Pattern Sync