Introduction

Section 1-1

6

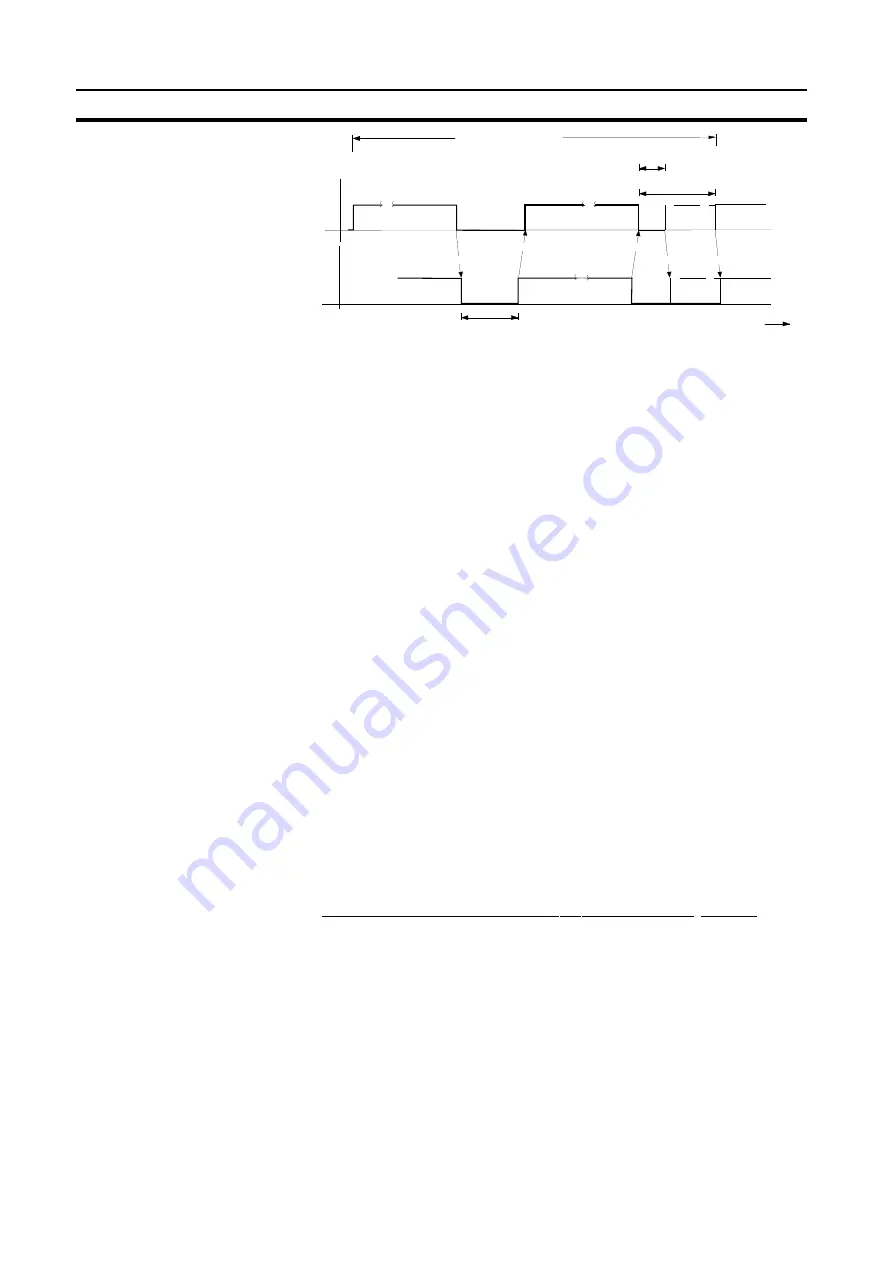

Master

Slave

receives

Slave Response

Send Pause

sends

Master Request

receives

Master Request

sends

Slave Response

Master Pause

sends

Master Request

receives

Master Request

Transaction

time

(1 -2 bit times)

Slave Pause

(2,5 to 5,5 bit times)

Security

A request or response will be judged invalid if it contains one of the following

types of error:

Start bit error

The initial pulse is not negative.

Alternating error

Two consecutive pulses do not have different polarity.

No information

Pulses are not detected in periods of

( * )

.

.

n

s

6

0 5

1 0

−

+

µ

.

Parity error

The sum of all information bits is not even.

End bit error

The last pulse is not positive.

Length error

Pulses are detected during the master or slave pause.

Upon an invalid or missing slave response, a master station will retry to

access the slave. If this fails, the slave will be taken out of the list of active

slaves. The master will cyclically try to re-initialise the slave in the inclusion

phase.

Performance

The cycle time of an AS-Interface network depends on the number of slaves

that the master has to exchange I/O data with. The AS-Interface specification

defines the maximum bus cycle time as follows:

if n = 33

n * Master request = n * (14 Bit) = n * 84

µ

s

=

2722

µ

s

+

n * Master pause

= n *

(3 Bit) = n * 18

µ

s (synchr. slave) =

594

µ

s

+

n * Slave response = n *

(7 Bit) = n * 42

µ

s

=

1386

µ

s

+ n * Send pause = n * (2 Bit) = n * 12

µ

s (min.)

= 396

µ

s

=

Tcycle

= n * (26 Bit) = n * 156

µ

s (min.)

=

5148

µ

s

where n is the number of all AS-Interface requests during data exchange in

the AS-Interface cycle and in the inclusion phase, including one repetition. In

normal operation, n will be the number of slaves plus 2.

With less than 31 slaves, the AS-Interface cycle time will be shorter. In

principle, each slave less will decrease the cycle time by 156

µ

s, but the

master is allowed to lengthen the send pause up to 500

µ

s, as long as the

total cycle time does not exceed the stated maximum.

To calculate the CQM1-ARM21’s cycle time, see 3-3, Performance.

Содержание CQM1-ARM21

Страница 1: ...CQM1 ARM21 AS Interface Master Unit OPERATION MANUAL Cat No W357 E1 1...

Страница 2: ......

Страница 3: ...CQM1 ARM21 AS Interface Master Unit Operation Manual Produced April 1999...

Страница 4: ...iv...

Страница 6: ...vi...

Страница 8: ...viii...

Страница 10: ...x...

Страница 30: ...AS Interface Network Installation Section 2 3 16...

Страница 38: ...Performance Section 3 3 24...

Страница 62: ...Setup Mode Section 4 5 48...

Страница 76: ...62...

Страница 80: ...66...

Страница 84: ......