Fabric DDR Subsystem

Microsemi ProprietaryUG0446 User Guide Revision 7.0

159

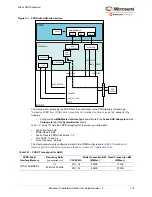

1.

Check the

Fabric External DDR Memory (FDDR)

check box

under the

Device Features

tab and

leave the other check boxes unchecked. The following image shows the

System Builder - Device

Features

tab.

Figure 82 •

System Builder - Device Features Tab

2.

Selecting the

Fabric External DDR Memory (FDDR)

check box in the

System Builder

performs

the following actions:

•

Instantiates the required IPs like CoreConfigMaster, CoreConfigP that initializes the FDDR

Controller.

•

Establishes the initialization path:

CoreConfigMaster

FIC_0

eNVM

FIC_2

CoreConfigP

APB bus of the FDDR

subsystem.

•

CoreConfigMaster (AHB Master) accesses the DDR configuration data stored in eNVM through

FIC_0

•

The configuration data is sent to CoreConfigIP through the FIC_2 master port

•

CoreConfigP sends the configuration data to APB bus of the FDDR subsystem

3.

Navigate to the

Memories

tab. Depending on the application requirement, select the memory

settings under the

General

tab as shown in the following image.

•

Memory Type can be selected as DDR2, DDR3 or LPDDR.

•

The Data width can be selected as 32- bit, 16-bit, or 8-bit. Refer to

supported data widths for various IGLOO2 device packages.

•

The SECDED (ECC) can be enabled or disabled.

•

Address Mapping - The register settings to perform mapping to system address bits for various

Row, Bank and Column combinations are automatically computed by the configurator using

address mapping option. The following table shows the supported range for Row, Bank and

Column.

Table 139 •

Supported Address Width Range for Row, Bank and Column

Width

DDR2

DDR3

LPDDR

Row Address

12-16

12-16

12-16

Bank Address

2-3

2-3

2-3

Column Address

9-12

9-12

9-12