FM33256B

Document Number: 001-86213 Rev. *C

Page 17 of 39

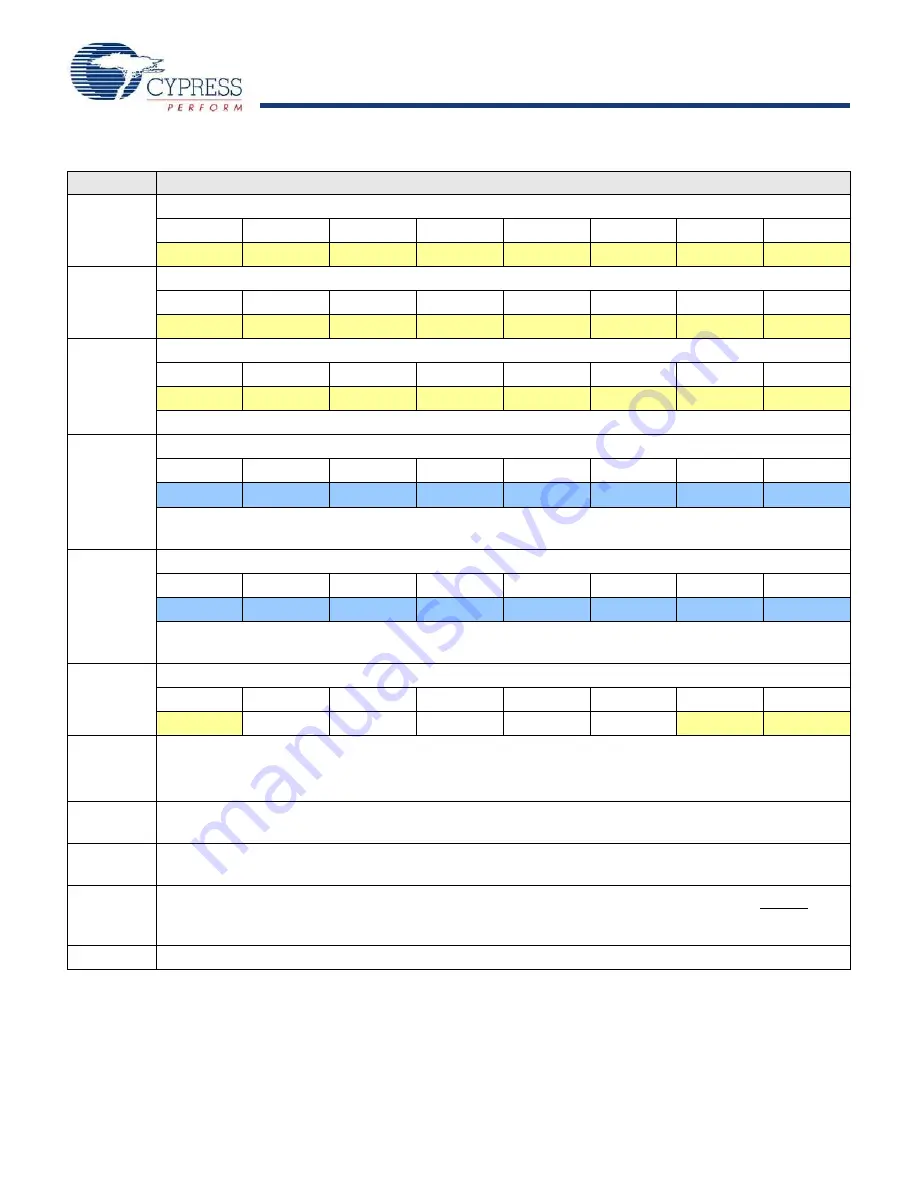

12h

Serial Number Byte 2

D7

D6

D5

D4

D3

D2

D1

D0

SN.23

SN.22

SN.21

SN.20

SN.19

SN.18

SN.17

SN.16

11h

Serial Number Byte 1

D7

D6

D5

D4

D3

D2

D1

D0

SN.15

SN.14

SN.13

SN.12

SN.11

SN.10

SN.9

SN.8

10h

Serial Number Byte 0

D7

D6

D5

D4

D3

D2

D1

D0

SN.7

SN.6

SN.5

SN.4

SN.3

SN.2

SN.1

SN.0

All serial number bytes are read/write when SNL = ‘0’, read-only when SNL = ‘1’. Nonvolatile.

0Fh

Event Counter Byte 1

D7

D6

D5

D4

D3

D2

D1

D0

EC.15

EC.14

EC.13

EC.12

EC.11

EC.10

EC.9

EC.8

Event Counter Byte 1. Increments on programmed edge event on CNT input. Nonvolatile when NVC = ‘1’,

Battery-backed when NVC = ‘0’, read/write.

0Eh

Event Counter Byte 0

D7

D6

D5

D4

D3

D2

D1

D0

EC.7

EC.6

EC.5

EC.4

EC.3

EC.2

EC.1

EC.0

Event Counter Byte 0. Increments on programmed edge event on CNT input. Nonvolatile when NVC = ‘1’,

Battery-backed when NVC = ‘0’, read/write.

0Dh

Event Counter Control

D7

D6

D5

D4

D3

D2

D1

D0

NVC

-

-

-

RC

WC

POLL

CP

NVC

Nonvolatile/Volatile Counter: Setting this bit to ‘1’ makes the counter nonvolatile and counter operates only when

V

DD

is greater than V

TP

. Setting this bit to ‘0’ makes the counter volatile, which allows counter operation under

V

BAK

or V

DD

power. If the NVC bit is changed, the counter value is not valid. Nonvolatile, read/write.

RC

Read Counter. Setting this bit to ‘1’ takes a snapshot of the two counter bytes allowing the system to read the

values without missing count events. The RC bit will be automatically cleared.

WC

Write Counter. Setting this bit to a ‘1’ allows the user to write the counter bytes. While WC = ‘1’, the counter is

blocked from count events on the CNT pin. The WC bit must be cleared by the user to activate the counter.

POLL

Polled Mode: When POLL = ‘1’, the CNT pin is sampled for 30 µs every 125 ms. If POLL is set, the NVC bit is

internally cleared and the CP bit is set to detect a rising edge. The RTC oscillator must be enabled (OSCEN = ‘0’)

to operate in polled mode. When POLL = ‘0’, CNT pin is continuously active. Nonvolatile, read/write.

CP

The CNT pin detects falling edges when CP = ‘0’, rising edges when CP = ‘1’. Nonvolatile, read/write.

Table 7. Register Description

(continued)

Address

Description