Source

Schematic Signal Name

Device/Pin

Number

I/O Standard

Description

J1.19

MAX_TX_DATA_LP_N3 MAX 10/ AA5

2.5V LVCMOS

Differential output data

Lane3 (low power,

negative terminal)

J1.17

MIPI_TX_DATA_HS_P4 MAX 10/ W2

1.8V HSTL

Differential output data

Lane4 (high speed,

positive terminal)

J1.16

MIPI_TX_DATA_HS_N4 MAX 10/ W1

1.8V HSTL

Differential output data

Lane3 (high speed,

negative terminal)

J1.17

MIPI_TX_DATA_HS_P4 MAX 10/ AB7

2.5V LVCMOS

Differential output data

Lane4 (low power,

positive terminal)

J1.16

MIPI_TX_DATA_HS_N4 MAX 10/ AB6

2.5V LVCMOS

Differential output data

Lane4 (low power,

negative terminal)

J1.14

MIPI_TX_CMOS_RST_

1V8

MAX 10/ T3

1.8V LVCMOS

Reset/Power Down

(1.8V)

J1.14

MIPI_TX_CMOS_RST_

3V3

MAX 10/ B10

3.3V LVCMOS

Reset/Power Down

(3.3V)

J1.13

MIPI_TX_CMOS_

SDATA_1V8

MAX 10/ N2

1.8V LVCMOS

Control Bus Data (1.8V)

J1.13

MIPI_TX_CMOS_

SDATA_3V3

MAX 10/ H12

3.3V LVCMOS

Control Bus Data (3.3V)

J1.12

MIPI_TX_CMOS_SCLK_

1V8

MAX 10/ N3

1.8V LVCMOS

Control Bus Clock (1.8V)

J1.12

MIPI_TX_CMOS_SCLK_

3V3

MAX 10/ J11

3.3V LVCMOS

Control Bus Clock (3.3V)

J1.11

MIPI_TX_CLK24MHz

Clock Generator /

U14.21

1.8V LVCMOS

24 MHz Reference Clock

Output

J1.10

MIPI_TX_GPIO1

MAX 10/ U3

1.8V LVCMOS

GPIO1

J1.9

MIPI_TX_GPIO2

MAX 10/ U2

1.8V LVCMOS

GPIO2

J1.7

MIPI_TX_GPIO3

MAX 10/ U4

1.8V LVCMOS

GPIO3

J1.6

MIPI_TX_GPIO4

MAX 10/ U5

1.8V LVCMOS

GPIO4

J1.5

MIPI_TX_GPIO5

MAX 10/ V3

1.8V LVCMOS

GPIO5

J1.33,

J1.32

1.8V_MIPITX

----

1.8V

1.8V

J1.36,

J1.35,

J1.34

3.3V_MIPITX

----

3.3V

3.3V

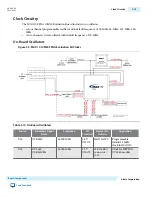

3-24

MIPI CSI-2 Transmitter

UG-20006

2016.02.29

Altera Corporation

Board Components

Send Feedback