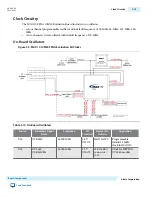

Board Reference

Schematic Signal

Name

MAX 10 FPGA Pin

Number

I/O Standard

Note 1

Description

J12.9

USER_LVDS_P0

AA10

DIFFIO_TX_RX_

B22P, High Speed

LVDS User I/O_0. Note 1

J12.10

USER_LVDS_P3

Y14

DIFFIO_TX_RX_

B37P, High Speed

LVDS User I/O_3. Note 1

J12.11

USER_LVDS_N0 Y10

DIFFIO_TX_RX_

B22N, High Speed

LVDS User I/O_0. Note 1

J12.12

USER_LVDS_N3 Y13

DIFFIO_TX_RX_

B37N, High Speed

LVDS User I/O_3. Note 1

J12.13

GND

----

----

Ground Reference for this

group of I/Os

J12.14

GND

----

----

Ground Reference for this

group of I/Os

J12.15

USER_LVDS_P1

W8

DIFFIO_TX_RX_

B13p, High Speed

LVDS User I/O_1. Note 1

J12.16

CLKOUT_LVDS_

P

V17

DIFFIO_TX_RX_

B57P or PLL_B_

CLKOUTP

Dual purpose pin. Either

User I/O or Clock output

ref. for this group of

LVDS channels

J12.17

USER_LVDS_N1 W7

DIFFIO_TX_RX_

B13n, High Speed

LVDS User I/O_1. Note 1

J12.18

CLKOUT_LVDS_

N

W17

DIFFIO_TX_RX_

B57N or PLL_B_

CLKOUTN

Dual purpose pin. Either

User I/O or Clock output

ref. for this group of

LVDS channels

J12.19

GND

----

----

Ground Reference for this

group of I/Os

J12.20

GND

----

----

Ground Reference for this

group of I/Os

J13.1

2.5V Power

----

----

Power Supply for

Connector J13

J13.2

2.5V Power

----

----

Power Supply for

Connector J13

J13.3

USER_LVDS_P5

V8

DIFFIO_TX_RX_

B7p, High Speed

LVDS User I/O_5. Note 1

3-10

General User Input/Output

UG-20006

2016.02.29

Altera Corporation

Board Components

Send Feedback