Clock Control GUI

This kit includes a Clock Control GUI application.

The Clock Control GUI application communicates over the JTAG bus to a test design running in the

FPGA. It shares the JTAG bus with other applications like the Nios II debugger and the SignalTap

®

II

Embedded Logic Analyzer. Because the Quartus II Programmer uses most of the bandwidth of the JTAG

bus, other applications using the JTAG bus might time out. Be sure to close the other applications before

attempting to reconfigure the FPGA using the Quartus II Programmer.

The Clock Control

The MAX 10 FPGA 10M50 Evaluation Board Clock Control application sets the programmable oscillators

to any frequency between 10 MHz and 200 MHz. It communicates with the MAX II device on the board

through the JTAG bus. The programmable oscillators are connected to the MAX II device through a 2-

wire serial bus.

To run the Clock Control GUI, perform the following steps:

1. Make sure Quartus II 14.1 or later version is installed.

2. Connect the USB cable to the MAX 10M50 FPGA Evaluation Board and power cycle the board.

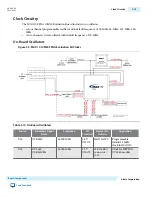

3. Double click the Clock Control GUI application and the interface shows as in the figure below.

4. Perform Default to set the default frequencies to the board: CLK0-24MHz, CLK1-24MHz,

CLK2-125MHz, CLK3-100MHz

5. Peform Read operation to get the current frequency setup.

6. If necessary, input new frequencies to each clock frequency fill-in box and perform Set New Freq to set

the board to the input clock frequency setup.

7. Select the Disable to disable any clock channel if needed.

Figure 3-4: The Si5338 Tab

UG-20006

2016.02.29

Clock Control GUI

3-15

Board Components

Altera Corporation

Send Feedback