14-5

IM 2558A-01EN

Status Reports

3

2

1

4

5

6

7

8

9

10

11

12

13

14

15

16

App

Index

14.4 Extended Event Register

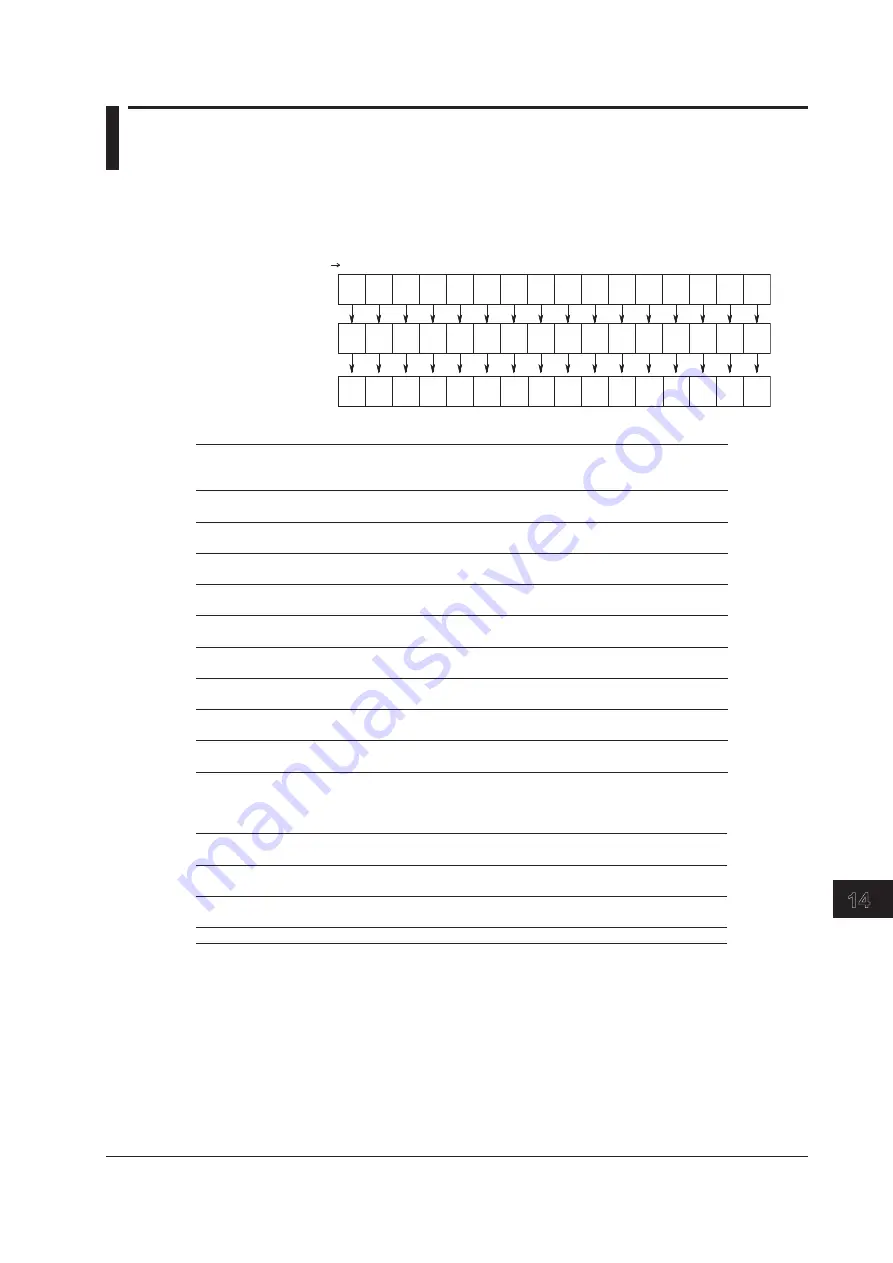

The extended event register receives information about changes in the condition register, which

indicates the instrument's internal condition. The information is the result of edge detection performed

by the transition filter.

EMR2

6

EMR4

7

5

4

3

2

1

0

EMR1 0

SCG

0

OUT EOS

FBE

OSC

8

0

9

EMR3

10

11

LMT

12

0

13

0

14

0

15

6

7

5

4

3

2

1

0

8

9

10

11

12

13

14

15

Condition register

:STATus:CONDition?

Transition filter

0

14

15

Extended event register

1

6

7

5

4

3

8

9

10

11

12

13

2

6

7

5

4

3

2

1

8

9

10

11

12

13

14

15

16

:STATus:FILTer<x>

{RISE│FALL│BOTH│NEVer}

:STATus:EESR?

FILTer<x>

The condition register bits are described below.

Bit 0

EOS

(End of Sweep)

Set to 1 during a sweep operation.

EOS changing from 1 to 0 indicates that sweeping has

been completed (held).

Bit 1

OUT

(Output ON)

Set to 1 during output.

Bit 3

SCG

(Source Change)

When the output value is changed, this bit is 1 until the

output reaches 90% of the value.

Bit 5

EMR1

(FAN Stop)

Set to 1 when the cooling fan stops.

Bit 6

EMR2

(Temprature Error)

Set to 1 when an abnormal temperature is detected

inside the 2558A.

Bit 7

EMR3

(Amplitude Temprature Error)

Set to 1 when an abnormal amplifier temperature is

detected inside the 2558A.

Bit 8

EMR4

(Internal Power Error)

Set to 1 when an internal power supply error is detected

in side the 2558A.

Bit 10

FBE

(Feedback Error)

Set to 1 when a feedback correction error is detected.

Bit 11

OSC

(Oscillating)

Set to 1 when an amplifier oscillation error is detected.

Bit 12

LMT

(Limting)

Set to 1 when an overload is detected.

The transition filter parameters detect changes in the specified condition register bits (numeric suffixes

1 to 16) and overwrite the extended event register in the following ways.

RISE

The specified extended event register bit is set to 0 when the corresponding condition

register bit changes from 0 to 1.

FALL

The specified extended event register bit is set to 1 when the corresponding condition

register bit changes from 1 to 0.

BOTH

The specified extended event register bit is set to 1 when the corresponding condition

register bit changes from 0 to 1 or from 1 to 0.

NEVer

Always zero.