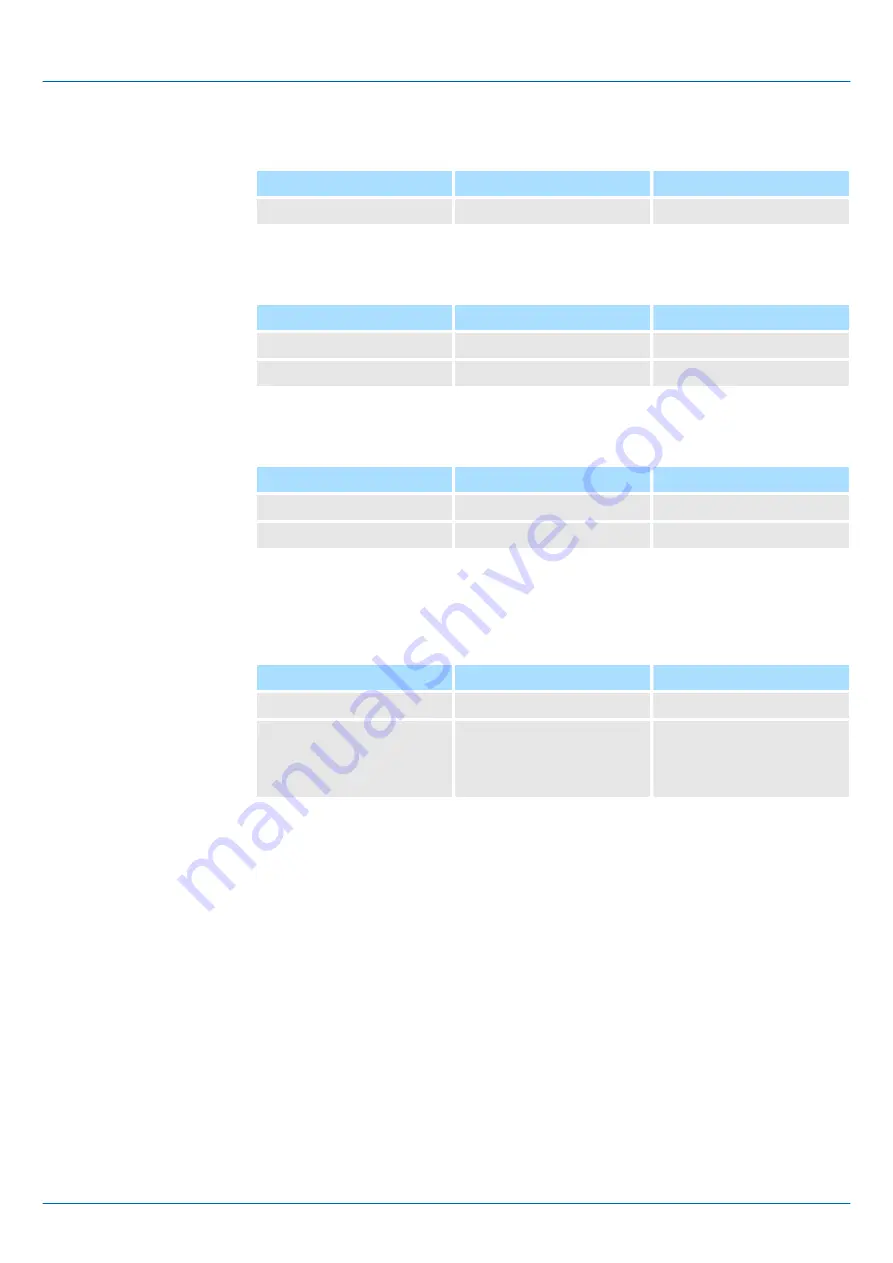

Gate control via SW gate, stopping (HW gate deactivated, gate function: Stop

count)

SW gate

HW gate

Reaction Counter

edge 0-1

deactivated

Continue

Gate control via SW/HW gate, canceling (HW gate activated, gate function: Cancel

count)

SW gate

HW gate

Reaction Counter

edge 0-1

1

Continue

1

edge 0-1

Restart with load value

Gate control via SW/HW gate, stopping (HW gate activated, gate function: Stop

count)

SW gate

HW gate

Reaction Counter

edge 0-1

1

Continue

1

edge 0-1

Continue

Gate control via SW/HW gate, operating mode "Count once" If the internal gate has been

closed automatically it may only be opened again under the following conditions:

SW gate

HW gate

Reaction I gate

1

edge 0-1

1

edge 0-1

(after edge 0-1

at HW gate)

edge 0-1

1

As soon as during a count process an edge 0-1 is recognized at the "Latch" input of a

counter, the recent counter value is stored in the according latch register. The latch value

may be accessed by the parameter LATCHVAL of the SFB 47. A just in LATCHVAL

loaded value remains after a STOP-RUN transition.

In the CPU a comparison value may be stored that is assigned to the digital output, to the

status bit "Status Comparator" STS_CMP and to the hardware interrupt. The digital

output may be activated depending on the count value and comparison value. A compar-

ison value may be entered by the parameter assignment screen form respectively by the

request interface of the SFB 47.

Gate control "Count once"

Latch function

Comparator

VIPA System 300S

+

Deployment I/O periphery

Counter > Counter - Additional functions

HB140 | CPU-SC | 313-5BF23 | en | 19-01

124