5.11.2

Function security

The CPUs include security mechanisms like a Watchdog (100ms) and a parameterizable

cycle time surveillance (parameterizable min. 1ms) that stop res. execute a RESET at the

CPU in case of an error and set it into a defined STOP state. The VIPA CPUs are devel-

oped function secure and have the following system properties:

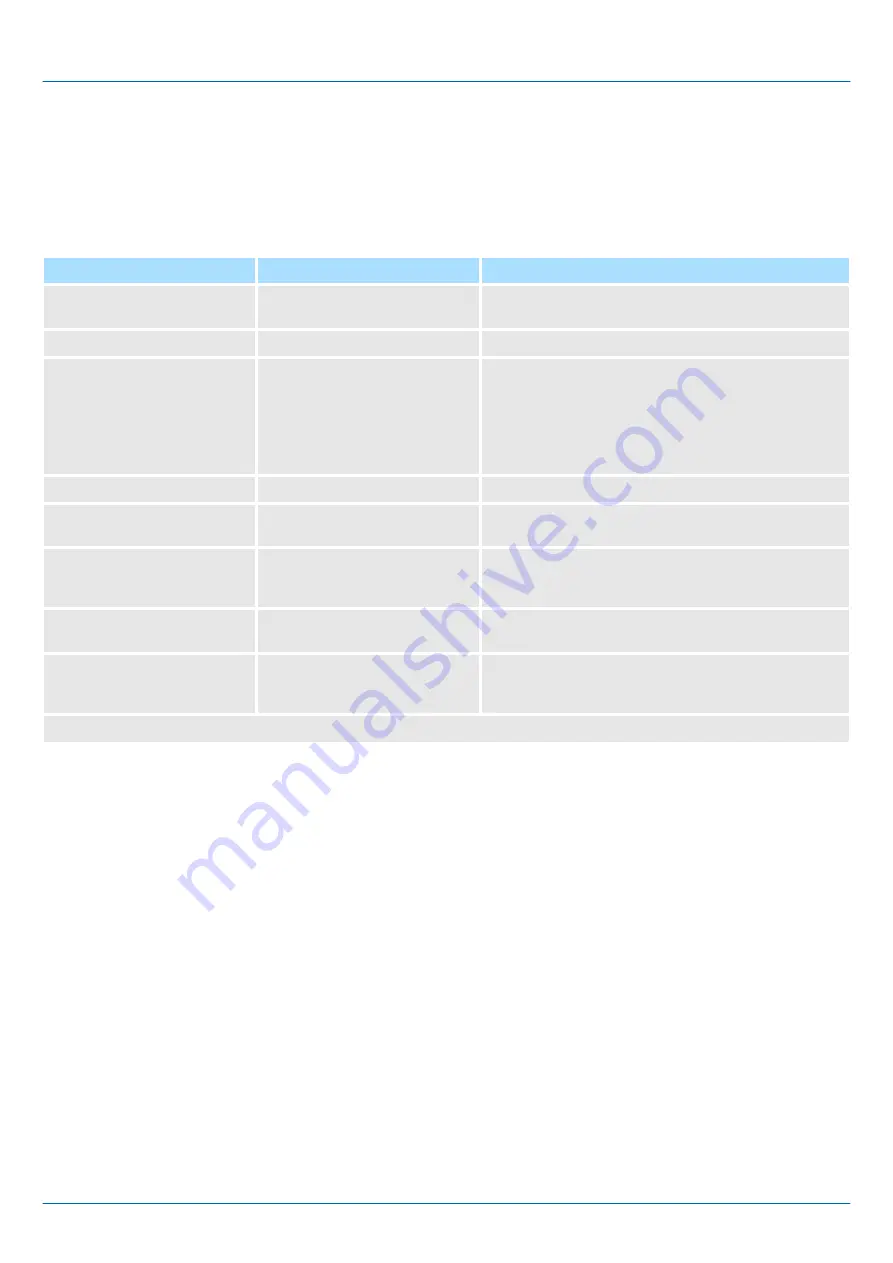

Event

concerns

Effect

RUN

®

STOP

general

BASP (Befehls-Ausgabe-Sperre, i.e. command output

disable) is set.

central digital outputs

The outputs are disabled.

central analog outputs

The outputs are disabled.

n

Voltage outputs issue 0V

n

Current outputs 0...20mA issue 0mA

n

Current outputs 4...20mA issue 4mA

If configured also substitute values may be issued.

decentral outputs

Same behavior as the central digital/analog outputs.

decentral inputs

The inputs are cyclically be read by the decentralized

station and the recent values are put at disposal.

STOP

®

RUN res. PowerON

general

First the PII is deleted, then OB 100 is called. After

the execution of the OB, the BASP is reset and the

cycle starts with: Delete PIO

®

Read PII

®

OB 1.

decentral inputs

The inputs are once be read by the decentralized sta-

tion and the recent values are put at disposal.

RUN

general

The program execution happens cyclically and can

therefore be foreseen: Read PII

®

OB 1

®

Write

PIO.

PII: Process image inputs, PIO: Process image outputs

VIPA System 300S

+

Deployment CPU 313-5BF23

Operating modes > Function security

HB140 | CPU-SC | 313-5BF23 | en | 19-01

70