5.3 Process Data Communication (Cyclic Communication)

5.3.4 Data Refreshing at CPU STOP

5-8

5.3.4 Data Refreshing at CPU STOP

When the CPU module has been set in the STOP status, the 264IF-01 Module carries out the following processing.

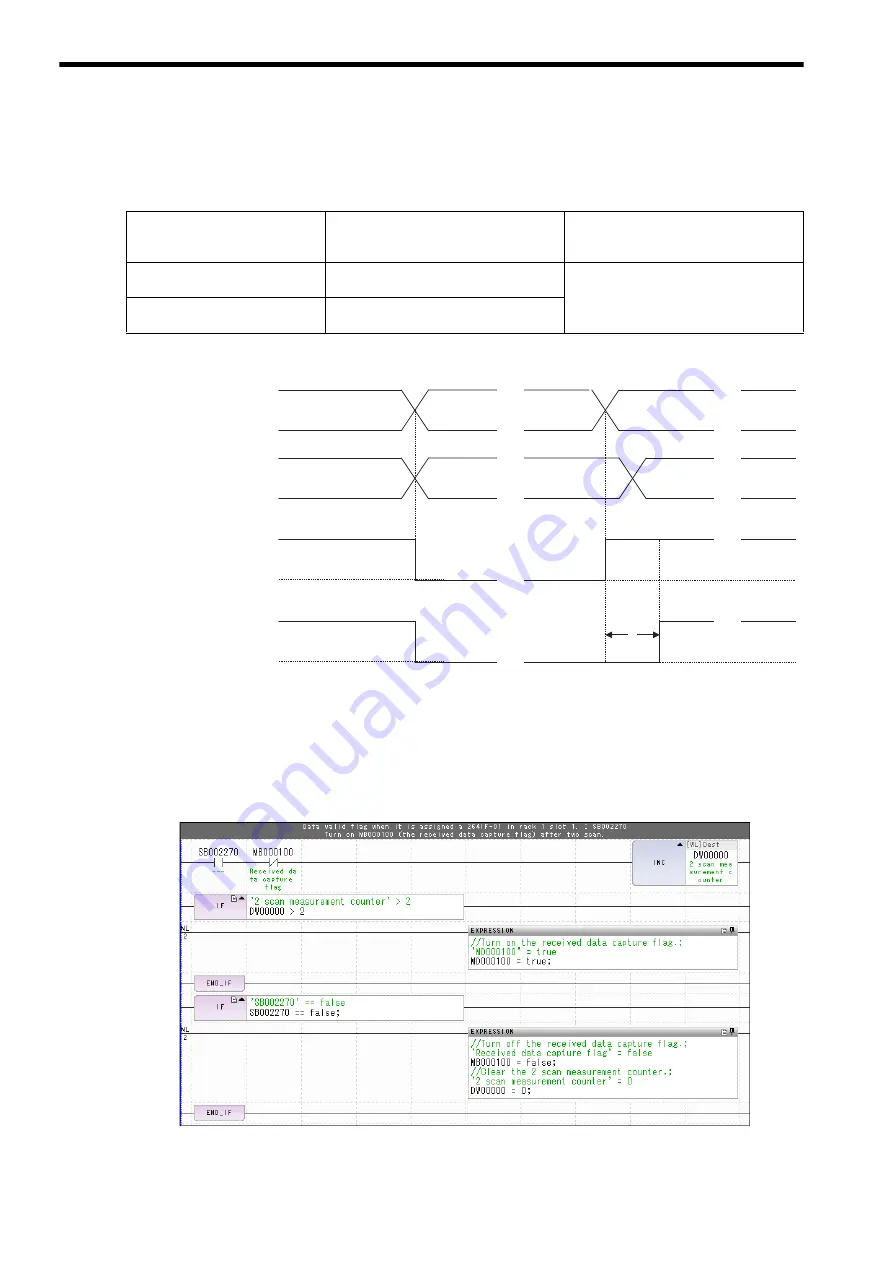

5.3.5 Input Data Read Timing

The Data Available Flag turns ON when EtherCAT communications change to the OPERATIONAL phase. The Ether-

CAT communications phase and Data Available Flag are not synchronized with the timing of reading the receive data.

Therefore, there is a delay between when the Data Available Flag turns ON and the start of reading the receive data.

For the application to allow for the delay in reading the receive data, create a Received Data Capture Flag to provide a

margin before reading the receive data after the Data Available Flag turns ON. Provide a margin of two scans (refer to

in the above figure).

A ladder programming sample for the Received Data Capture Flag is given below.

Table 5.2 Data Refreshing at CPU STOP

“Output status at CPU STOP”

Setting in the 264IF-01 Module’s

Detailed Definitions

Output Data

Input Data

Hold

The final data output before CPU STOP is

continued.

There is no refreshing of input registers.

At input registers, the final data before CPU

STOP is held.

Zero clear

Output of “0” data is continued during the

CPU STOP status.

ON

OFF

㨪

㨪

OPERATIONAL

INIT

PRE-OPERATIONAL

SAFE-OPERATIONAL

㨪

㨪

㨪

㨪

OPERATIONAL

㨪

㨪

㨪

㨪

㨪

㨪

ON

OFF

㨪

㨪

㨪

㨪

Receive data 0 cleared.

㨪

㨪

㨪

㨪

Receive data normal.

㨪

㨪

㨪

㨪

Receive data normal.

EtherCAT communications phase

(system register)

Status of receive data

(input registers)

Data Available Flag status

(system register)

Receive data read flag status

(Created in user application

as required.)