60

Virtex-5 RocketIO GTP Transceiver User Guide

UG196 (v1.3) May 25, 2007

Chapter 5:

Tile Features

R

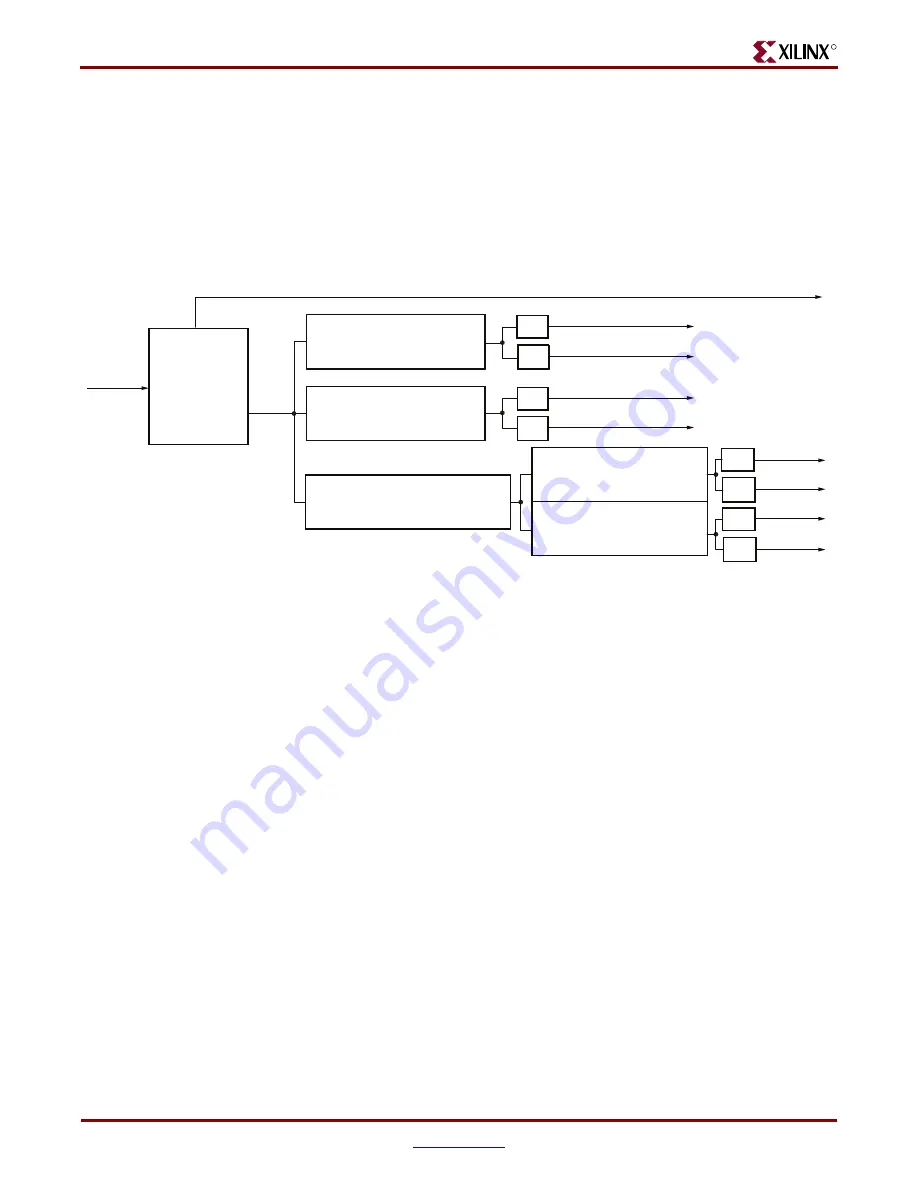

Shared PMA PLL

Overview

This section describes the shared PMA PLL of the GTP_DUAL tile, which is illustrated in

. Each GTP_DUAL tile includes one shared PMA PLL used to generate a high-

speed serial clock from a high-quality reference clock (CLKIN). The high-speed clock from

this block drives the TX and RX PMA blocks for both GTP transceivers in the tile.

The shared PMA PLL generates the high-speed clock (PLL clock) used by both transceivers

in the GTP_DUAL tile. After the shared PMA PLL rate is set (PLL clock), the TX and RX

output dividers (dividers ending with _OUT) are set to determine the TX and RX line rates

for each transceiver.

Ports and Attributes

defines the shared PMA PLL ports.

Figure 5-1:

Shared PMA PLL Detail

Di

v

ide

b

y

PLL_TXDI

V

SEL_OUT_0

(4)

= [1,2,4]

Di

v

ide

b

y

PLL_TXDI

V

SEL_OUT_1

(4)

= [1,2,4]

Di

v

ide

b

y

PLL_TXDI

V

SEL_COMM_OUT

(4)

= [1,2,4]

Shared PLL

PLL

Clock

CLKI

N

=

REFCLOCK

REFCLOCKOUT

PLLRESET

PLLPO

W

ERDO

WN

PLL_DI

V

SEL_FB

(5)

= [1,2,3,4,5]

PLL_DI

V

SEL_REF = [1,2]

I

N

TDATA

W

IDTH

GTP0 RX Serial Clock

x2

GTP0 RX Parallel Clock

GTP0 TX

Serial Clock

GTP0 TX

Parallel Clock

GTP1 TX

Serial Clock

GTP1 TX

Parallel Clock

GTP1 RX Serial Clock

GTP1 RX Parallel Clock

/

W

(3)

/

W

(3)

x2

(1)

x2

(1)

x2

(2)

/

W

(3)

x2

(2)

/

W

(3)

Di

v

ide

b

y

PLL_RXDI

V

SEL_OUT_1 = [1,2,4]

Di

v

ide

b

y

PLL_RXDI

V

SEL_OUT_0 = [1,2,4]

UG196_c5_01_030307

Notes:

1. The Serial-In Parallel-Out (SIPO) block in each receiver uses both edges of the high-speed clock. As a result, the effective RX serial

clock rate is 2 x PLL Clock/PLL_RXDIVSEL_OUT_n.

2. The Parallel In Serial Out (PISO) block in each transmitter uses both edges of the high-speed clock. As a result, the effective TX

serial clock rate is 2 x PLL Clock/[PLL_TXDIVSEL_OUT_n, PLL_TXDIVSEL_COMM_OUT].

3. The parallel clock rate is divided to match the internal datapath width. When INTDATAWIDTH =

0

(8-bit internal width), W = 4.

When INTDATAWIDTH =

1

(10-bit internal width), W = 5.

4. Refer to

about the correct setting of these attributes for specific loopback modes.

5. When INTDATAWIDTH =

0

, PLL_DIVSEL_FB can only be set to 1, 2, or 4. For PLL_DIVSEL_FB =

1

set PCS_COM_CFG to

28’

h

1680A07

, otherwise set to

28’h1680A0E

(default).