TXZ Family

Serial Peripheral Interface

2019-02-28

12 / 67

Rev. 3.0

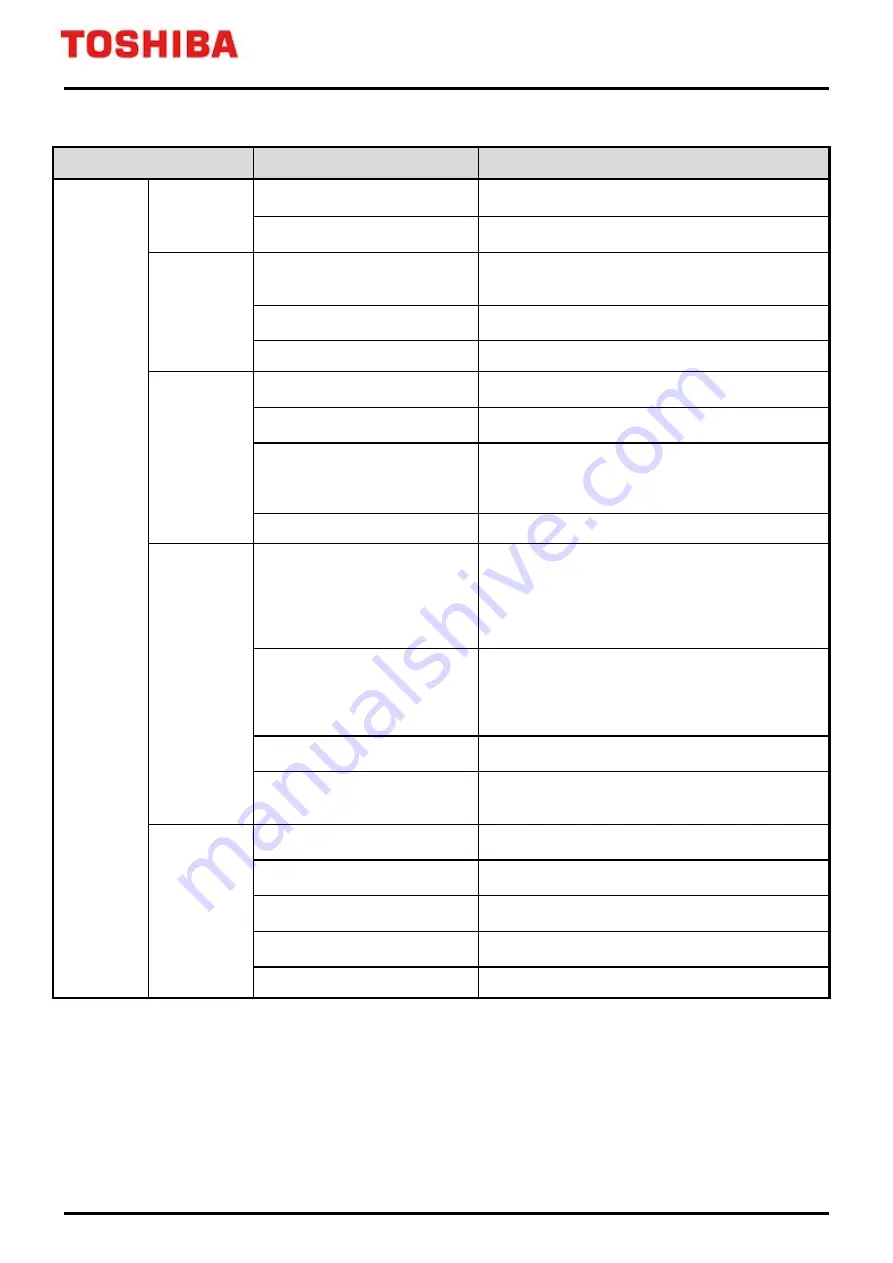

Table 1.3 Functional outline (SIO mode, master)

Function classification

Function

A Functional Description or the range

SIO mode

(Master)

Transmission

speed

Control

Prescaler dividing selection

The clock inputted from the prescaler can be

divided 1/1,1/2,1/4..up to 1/512.

Baud rate generator

The input clock to baud rate generator.

dividing 1/N x 1/2 (N= 1 to 16)

Data

Format

Data length

The data length can be setup in a 1-bit unit.

8 to 32bits (with no parity)

7 to 31bits (with parity)

Parity

Selection of with parity/without parity is possible.

Selection of even parity/odd parity is possible.

The direction of data transfer

Selection of the LSB first/ MSB first is possible.

Transceiver

Control

FIFO number of section

Transmission: 8 steps (16bits), 4 steps (32bits)

Reception: 8 steps (16bits), 4 steps (32bits)

Communication Operation

mode

Full duplexes (transmission and reception),

transmission, reception

Transfer mode

Single transfer (one burst transfer)

Burst transfer (2 to 255 times transfer)

Continuously transfer (No limit of transfer times

specification)

Data sampling timing

Data is sampled with 2

nd

edge.

Ganged

Control

Interruption

Transmit interrupt (Transmit completion interrupt,

Transmit FIFO interrupt)

Receive interrupt (Receive completion interrupt,

Receive FIFO interrupt)

Error Interrupt (Vertical parity error interrupt,

Trigger error interrupt)

Various status detection

TSPI modify status,

Transmit shift operation, Transmit completion,

Transmit FIFO fill level/ empty detection,

Receive operation,

Receive completion, Receive

FIFO fill level /full detection

DMA demand

Transmit:Single DMA request, Burst DMA request

Receive: Single DMA request, Burst DMA request

Trigger communication control

Starting communication by trigger. Refer to the

"Product Information" on a reference manual for a

trigger source.

Special

Control

Output level of TSPIxTXD

during an idle term

High, Low, a last bit data hold, Hi-z

Polarity of TSPIxSCK during an

idle term

It is Low to during idle term.

It is High to during idle term.

Interval time between frames at

the time of burst transfer.

0 x TSPIxSCK cycle to 15 x TSPIxSCK cycles

Idle time at the time of

continuously transfer

1 x TSPIxSCK cycle to 15 x TSPIxSCK cycles

Software reset

Reset by software is possible.