Chapter 3

E300 Power Modes

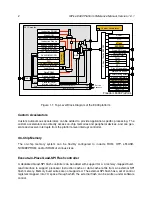

This chapter describes the different power modes available on E300 systems. E300 systems

currently support three power modes: Run, Wait, and Sleep.

Run Mode

Run mode corresponds to regular execution where the processor is running. Power consumption

can be adjusted by varying the clock frequency of the processor and peripheral bus, and by en-

abling or disabling individual peripheral blocks. The processor exits run mode by executing a “Wait

for Interrupt” (WFI) instruction.

Wait Mode

When the processor executes a WFI instruction it enters Wait mode, which halts instruction exe-

cution and gates the clocks driving the processor pipeline. All state is preserved in the system.

The processor will resume in Run mode when there is a local interrupt pending or when the PLIC

sends an interrupt notification. The processor may also exit wait mode for other events, and soft-

ware must check system status when exiting wait mode to determine the correct course of action.

Sleep Mode

Sleep mode is entered by writing to a memory-mapped register

pmusleep

in the power-

management unit (PMU). The

pmusleep

register is protected by the

pmukey

register which must

be written with a defined value before writing to

pmusleep

.

The PMU will then execute a power-down sequence to turn off power to the processor and main

pads. All volatile state in the system is lost except for state held in the AON domain. The main

output pads will be left floating.

Sleep mode is exited when an enabled wakeup event occurs, whereupon the PMU will initiate

a wakeup sequence. The wakeup sequence turns on the core and pad power supplies while

asserting reset on the clocks, core and pads. After the power supplies stabilize, the clock reset

is deasserted to allow the clocks to stabilize. Once the clocks are stable, the pad and processor

resets are deasserted, and the processor begins running from the reset vector.

Software must reinitialize the core and can interrogate the PMU

pmucause

register to determine

the cause of reset, and can recover pre-sleep state from the backup registers. The processor

7

Summary of Contents for E300

Page 1: ...SiFive E300 Platform Reference Manual Version 1 0 1 c SiFive Inc ...

Page 2: ...2 SiFive E300 Platform Reference Manual Version 1 0 1 ...

Page 4: ...ii SiFive E300 Platform Reference Manual Version 1 0 1 ...

Page 12: ...4 SiFive E300 Platform Reference Manual Version 1 0 1 ...

Page 14: ...6 SiFive E300 Platform Reference Manual Version 1 0 1 ...

Page 22: ...14 SiFive E300 Platform Reference Manual Version 1 0 1 ...

Page 32: ...24 SiFive E300 Platform Reference Manual Version 1 0 1 ...

Page 40: ...32 SiFive E300 Platform Reference Manual Version 1 0 1 ...

Page 56: ...48 SiFive E300 Platform Reference Manual Version 1 0 1 ...

Page 60: ...52 SiFive E300 Platform Reference Manual Version 1 0 1 ...