DX-SX1H

– 62 –

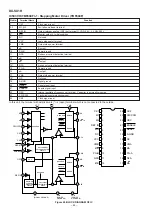

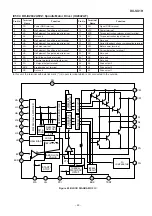

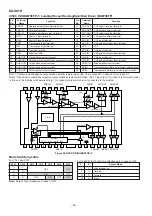

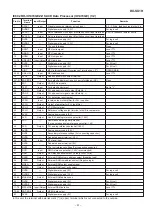

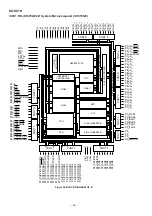

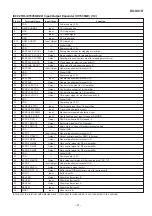

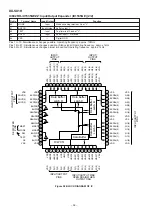

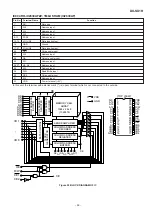

IC901 VHiCXD2751Q-1: SACD Playback Signal Processor (CXD2751Q) (1/2)

1

XSRQ

Output

Output terminal for data request to be input in the front end processor.

2

XSHD

Input

Input terminal for header flag to be output from the front end processor.

3

VDD

—

Power supply terminal, +3.3V

4

VSS

—

Ground terminal

5

SDCK

Input

Input terminal for data transmitting clock to be output from the front end processor

6

SMUTE

Input

Soft mute terminal

H: Soft mute of audio output, L: Released

7

XMSLAT

Input

Latch input terminal for microcomputer serial communication

Latches addresses and data when this terminal rises.

8

MSCK

Input

Shift clock input terminal for microcomputer serial communication

Inputs and shifts the serial input data when the clock to be input in this terminal rises.

Read-out data change when the clock to be input in this terminal falls.

9

MSDATI

Input

Data input terminal for microcomputer serial communication (Microcomputer -> CXD2751Q)

Inputs serial data and addresses for communication.

10

MSDATO

Output

Data input terminal for microcomputer serial communication (CXD2751Q -> Microcomputer)

High impedance except during output

11

MSREDY

Output

Ready-to-output flag for microcomputer serial communication. Outputs "L", if complete.

Open drain.

12*

XMSDOE

Output

Data enable terminal for microcomputer serial communication

Makes this terminal active when using the try state buffer outside.

13

XRST

Input

Resets entire IC when reset terminal is "L".

Clock which is output from output terminals EXCKO1, EXCKO2, and LRCK does not stop during reset.

14

MCKI

Input

Master clock input terminal

Inputs clock of 512Fs (22.579 MHz) or 768Fs (33.869 MHz).

15

VSS

—

Ground terminal

16

CK75S

Input

Master clock select terminal. Selects "H" in case of 768Fs and "L" in case of 512Fs.

17

EXCKO1

Output

External output clock terminal 1. Outputs 768Fs/512Fs/256Fs/128Fs according to setting.

18*

EXCKO2

Output

External output clock terminal 2. Outputs 768Fs/512Fs/256Fs/128Fs according to setting.

19*

LRCK

Input/Output

IFs (44.1kHz) clock input/output terminal. Selects master/slave according to setting.

20*

NC

—

Not used

21*

MNT2

Output

Monitor output terminal. Outputs partial internal operation according to setting.

22

TRST

Input

Reset terminal for test. Inputs power-on reset signal or fixed at "L".

23

TCK

Input

Test clock input terminal. Fixed at "L".

24*

TDI

Input

Test input terminal. Open

25*

TENA1

Input

Test input terminal. Open

26*

TDO

Output

Test input terminal. Open

27

VST

—

Test ground terminal. Connected to ground

28

VDD

—

Power supply terminal, +3.3V

29

VSS

—

Ground terminal

30*, 31* MNT1, MNT0

Output

Monitor output terminal. Outputs partial internal operation according to setting.

32*

XBIT

Output

DST related monitor terminal. Not connected.

33*

F75HZ

Output

75Hz clock output terminal

34*

SUPDAT

Output

Supplementary data serial output terminal

35*

XSUPAK

Output

Supplementary data effective flag terminal

Outputs "L" when supplementary data are effective.

36*

SUPEN

Output

Supplementary data byte-unit enable output terminal

Changes to "H" at the break of 1 byte (8 bits) of serial data.

37

TEST1

Input

Test input terminal. Fixed at "L".

38

VSS

—

Ground terminal

39

TEST2

Input

Test input terminal. Fixed at "L".

40, 41

VSS

—

Ground terminal

42*

BCKD

Input/Output

Phase reference signal input/output terminal for DSD data phase modulation output

Input/output according to setting

43*-45*

NC

—

Not used

Pin No. Terminal Name Input/Output

Function

In this unit, the terminal with asterisk mark (*) is (open) terminal which is not connected to the outside.