DX-SX1H

– 58 –

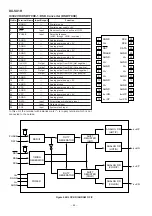

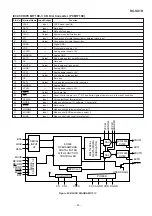

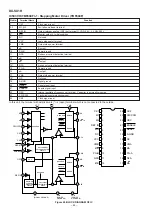

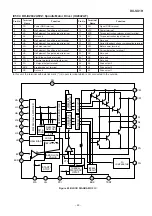

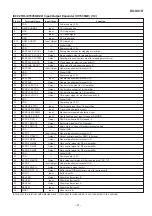

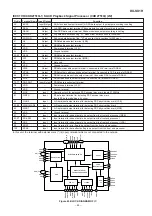

IC802 RH-iX1535GEZZ: Input/Output Expander (IX1535GE) (2/2)

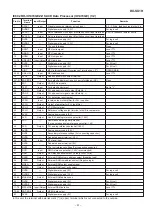

60

MODE

Input

Mode switching terminal. Fix at "L".

61

BUFCO

Input/Output

Buffer output C

62

TEST

Input

Test terminal. Fixed at "L".

63

BUFCI

Input

Buffer input C. Not used.

64

VSS

—

Digital GND

Pin No.

Terminal Name

Input/Output

Function

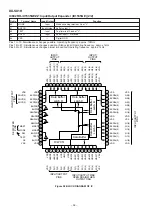

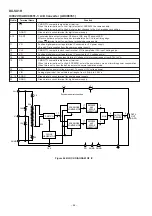

Figure 58 BLOCK DIAGRAM OF IC

Pins 1 to 15: Simultaneous changes possible. Operating frequency: approx. 10MHz

Pins 18 to 47: Simultaneous changes possible. (Static signal) Operating frequency: approx. 1kHz

Pins 50 to 57: Simultaneous changes almost impossible. Operating frequency: approx. 1kHz

Data Buffer

Latch D

Data Buffer

Latch C

Data Buffer

Latch B

Data Buffer

Latch A

Data Buffer

R/W CTL

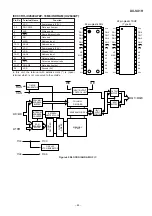

49

50

51

52

53

54

55

56

57

58

59

60

61

62

63

64

32

48 47 46 45 44 43 42 41 40 39 38 37 36 35 34 33

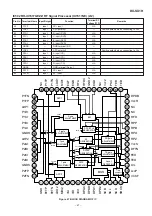

1

2

3

4

5

6

7

8

9

10 11 12 13 14 15 16

31

30

29

28

27

26

25

24

23

22

21

20

19

18

17

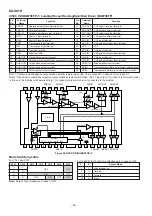

VDD

EXPD(3)

EXPD(4)

EXPD(5)

BUFDO

BUFDI

SBUFBO

SBUFBI

SBUFAO

SBUFAI

MRST

MODE

BUFCO

TEST

BUFCI

VSS

VSS

EXPBL(3)

EXPBL(2)

EXPBL(1)

EXPBL(0)

EXPAU(3)

EAPAU(2)

VDD

VSS

EXPAU(1)

EXPAU(0)

EXPAL(3)

EAPAL(2)

EXPAL(1)

EAPAL(0)

VDD

VSS

Q2(3)

Q2(2)

Q2(1)

Q2(0)

Q1(7)

Q1(6)

VDD

VSS

Q1(5)

A1(4)

Q1(3)

Q1(2)

Q1(1)

Q1(0)

VDD

VDD

SOUT(3)

SOUT(4)

SOUT(5)

MRST

MODE

SEL

TEST

CK

VSS

VSS

EXPD(2)

EXPD(1)

EXPD(0)

EXPC(5)

EXPC(4)

EXPC(3)

VSS

EXPC(2)

EXPC(1)

EXPC(0)

EXPBU(3)

EXPBU(2)

EXPBU(1)

EXPBU(0)

VDD

VDD

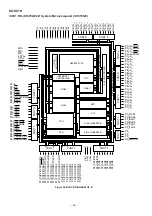

HADR0

HADR1

HADR2

HCS

HWR

HRD

HDAT0

HDAT1

HDAT2

HDAT3

HDAT4

HDAT5

HDAT6

HDAT7

VSS

VDD

D(0)

D(1)

D(2)

D(3)

D(4)

D(5)

D(6)

D(7)

S1(0)

S1(1)

S1(2)

S1(3)

S1(4)

S1(5)

VSS

VSS

SOUT(2)

SOUT(1)

SOUT(0)

S2(5)

S2(4)

S2(3)

VSS

S2(2)

S2(1)

S2(0)

Q2(7)

Q2(6)

Q2(5)

Q2(4)

VDD

INPUT/

OUTPUT

PINS

INPUT/OUTPUT

PINS

INPUT/OUTPUT PINS

OPEN DRAIN WHEN

OUTPUTTING

INPUT/OUTPUT

PINS

INPUT/OUTPUT

PINS

INPUT/

OUTPUT

PINS

DEDICATED

PINS