DX-SX1H

– 13 –

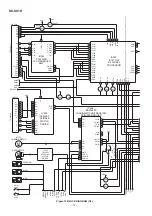

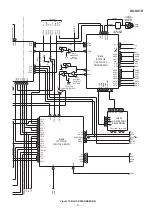

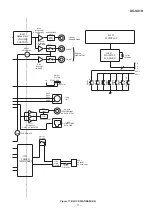

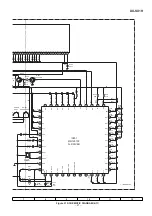

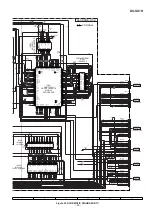

Figure 13 BLOCK DIAGRAM (2/6)

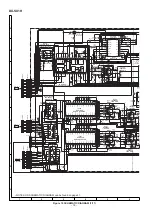

IC507

HC4053FS

ANALOG SWITCH

1/3

HC4053FS

ANALOG SWITCH

IC507

HC4053FS

ANALOG SWITCH

2/3

IC601

AD8052AR

DUAL

OPE AMP.

IC505

NJM324V

4-CIRCUIT

OPE AMP.

IC604

TC7W74FU

1/2 DIVIDING

X602

54MHz

IC605

TC7WU04FU

3-CIRCUIT

INVERTER

IC603

SC514870SJ

4Mbit DRAM

IC606

IX1473GE

DIGITAL SERVO

IC602

IX1474GE

SACD DATA

PROCESSOR

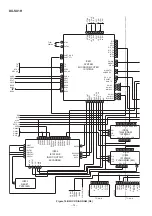

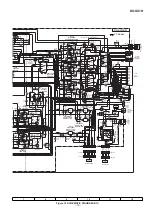

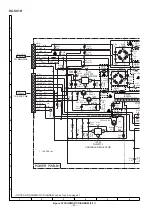

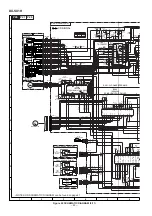

02

7GE

GNAL

ESSOR

DOUT

BCK

IPF

LRCK

AOUT

RF_LT

BUCK

EMPH

BUS3

SBSY

CCE

0

DATA

PLCK

DATA

PLCK

D15

8

D

18

H1,0

HDRD

HCEN

D8

SDCK

RSTN

SREQ

SVAL

HINT

HDWT

SD7

SOSO

SD0

SERR

15

,

27

24

2

~ 5

A9R A0~A3

A4~A8

16

10

33MHz

MCK1

XO

74

59

68

88

50

53

24MHz

54MHz

9

3

4

5

12

13

14

INV

Buff

Vref

TO IC901

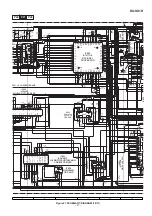

WARF

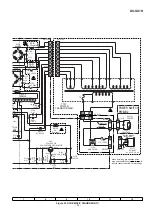

TP506

4

LDO2

45

LDO1

4

DOUT

DMO

52

51

48

23

RAS

8

WE

22

7

OE

RVDD

RASN

53

47

55

MWEN

56

ED7

CK54M

3

CK27M

32 24

1

PLCK

RF

Vref

TE

AGND

TP510

FE

TP507

TP509

TP508

TP513

PLCK

DATA

DGND

TP511

TP512

52

SEL

Vref

STCK

STDA

97

98

D

9

10

11

23

22

HCEN

HDRD

H1,0

HINT

SD0

90

89

85

79

21

SERR

8

SOSO

SD7

HDWT

SDCK

RSTN

SVAL

SREQ

91

92

94

95

24

32

100

3

6

IPF

BCK

AOUT

LRCK

CCE

SBSY

BUS0

~

BUS

3

BUCK

EMPH

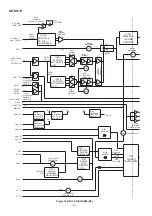

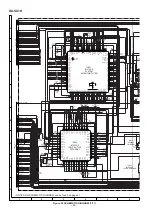

92

91

85

13

99

SCD

SCL

SCB

VRCK

13

14

15

16

28

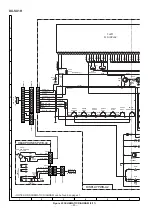

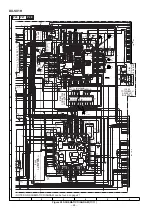

RFO

EQB

EQF

42

43

TEB

FEO

TEO

RPO

RPZ

LVL

19

33

21

24

25

20

TE

LVL

FE

RFRP

59

DFCT

SHC

JOO

56

67

61

19

TESIO1

62

TESIO0

JO2

JO3

47

48

TEBC

50

FMO

DMO

TEIN

FEIN

TEZI

SBAD

39

42

38

41

RFRP

RFIN

RFZI

RFCT

35

36

33

37

FOO

TRO

44

43

RFIN

DVR

54

9

CAS

2

13

~

~

~

~

~

~

~

~

~

20

MOEN

MA9~MA0

I/O1~ I/O4 I/O5~ I/O8

DMO

FOON

7